Interrupt processing method and microcontroller

A processing method and technology of a processing device, applied in the directions of multi-programming device, program startup/switching, etc., can solve the problems of long response time to interrupt, low interrupt processing efficiency, slow command running speed, etc. The effect of reducing the time to respond to interruptions and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0026] This embodiment provides an interrupt processing method. In this embodiment, an 8051 microcontroller is used as an example for illustration.

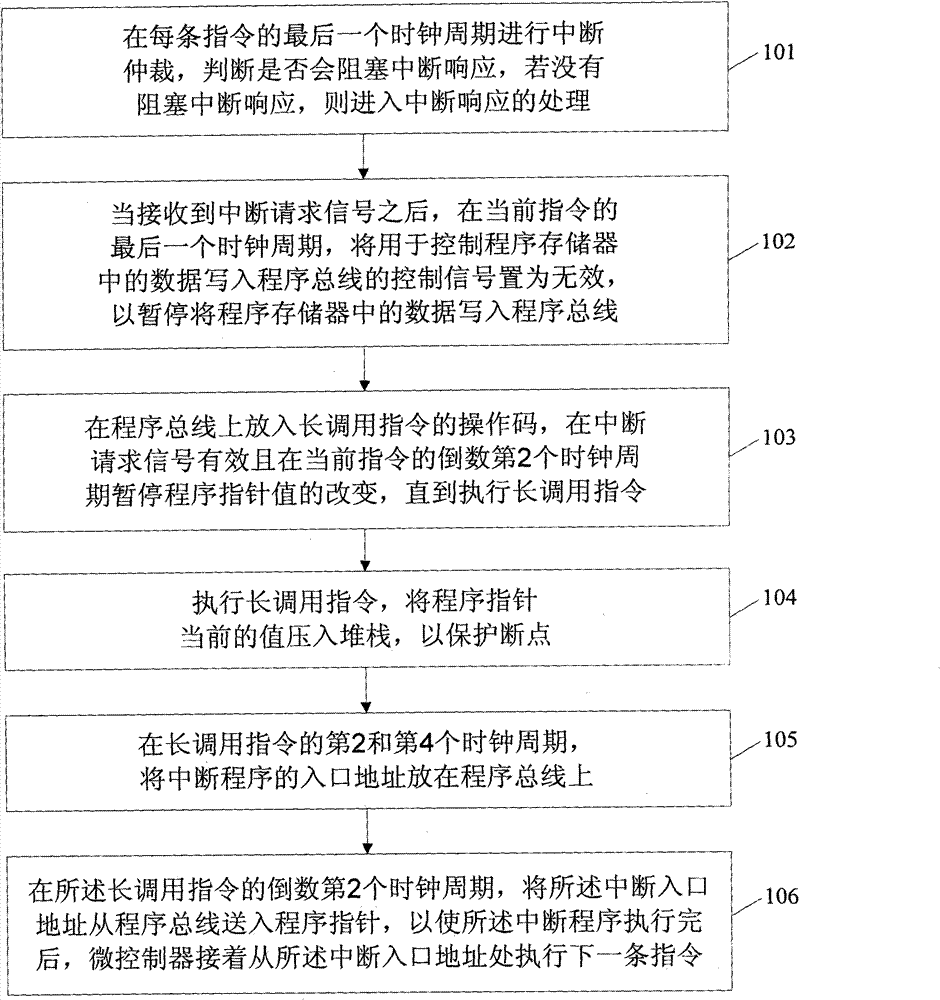

[0027] Such as figure 1 As shown, the method includes:

[0028] 101. Interrupt arbitration is performed in the last clock cycle of each instruction to determine whether the interrupt response will be blocked, and if the interrupt response is not blocked, enter the processing of the interrupt response.

[0029] Specifically, the interrupt timing module performs interrupt arbitration at the last clock cycle of each instruction execution, that is, when SL=1, and when it is found that a certain interrupt can be responded to, the interrupt flag bit is pulled high, causing an interrupt request in the next clock cycle The signal becomes high, indicating that the processing of the interrupt response is entered. Since the next instruction has been read before the interrupt arbitration in the SL state, the next instruction read is execut...

Embodiment 2

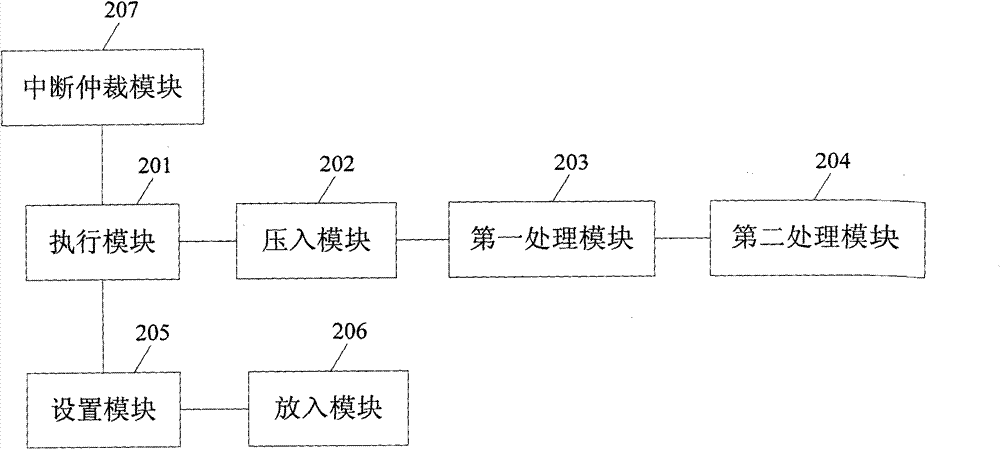

[0047] This embodiment provides a microcontroller, such as figure 2 As shown, the microcontroller includes:

[0048] The execution module 201 is configured to execute a long call instruction when there is a corresponding interrupt program, wherein the long call instruction includes 7 clock cycles;

[0049] Push module 202, used to push the current value of the program pointer into the stack to protect the breakpoint;

[0050] The first processing module 203 is used to send the corresponding interrupt entry address into the program bus in the second and fourth clock cycles of the long call instruction;

[0051] The second processing module 204 is configured to send the interrupt entry address from the program bus into the program pointer in the penultimate second clock cycle of the long call instruction, so that after the execution of the interrupt program is completed, from the interrupt Execute the next instruction at the entry address.

[0052] Further, as shown in Figur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com