Register circuit realizing grouping addressing and read write control method for register files

A register file and register bank technology, applied in the direction of machine execution devices, etc., can solve problems such as the impact of processor performance, and achieve the effects of low power consumption, providing power consumption, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

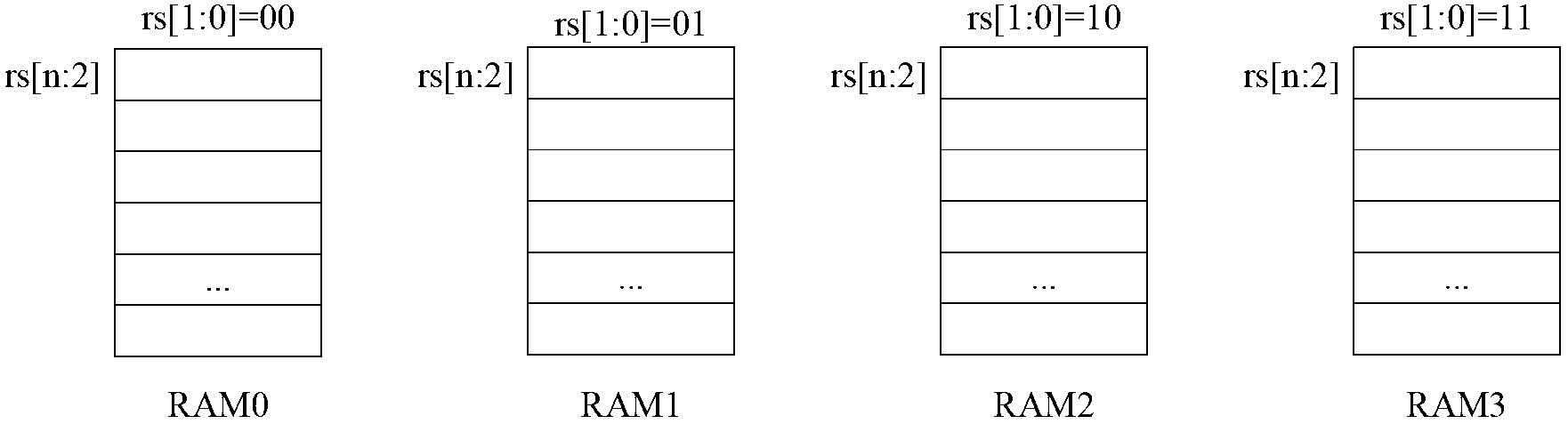

[0036] A register file group addressing and read-write control method for a floating-point coprocessor comprises the following two steps:

[0037] (1) Register file group addressing

[0038] The reason why multiple clock cycles are required for operand preparation and result storage back to the register during high-precision floating-point calculation is that the register bit width is 32 bits, and each time a register is read or written, while double and quad precision need to be read separately Or two and four registers are written, which requires multiple register reads or writes. In order to reduce the number of read or write cycles, it is necessary to realize the simultaneous reading and writing of multiple registers. The original unified register file is grouped, and each group is implemented using a RAM block with a "one read, one write" port. In this way, each Access to multiple registers can be realized through the corresponding read and write control methods during t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com