Wafer holding mechanism, wafer holding system and wafer matched with wafer carrier

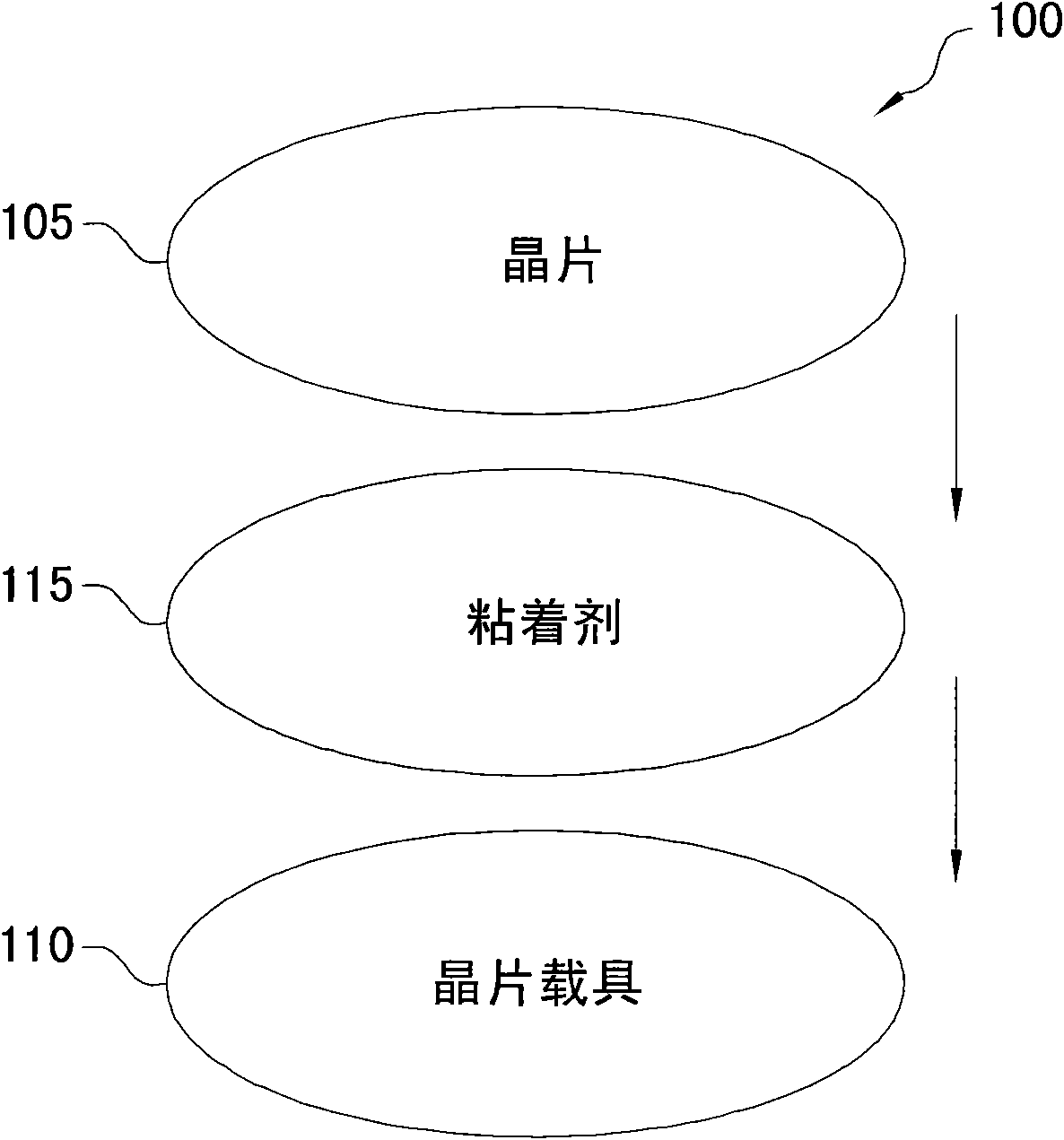

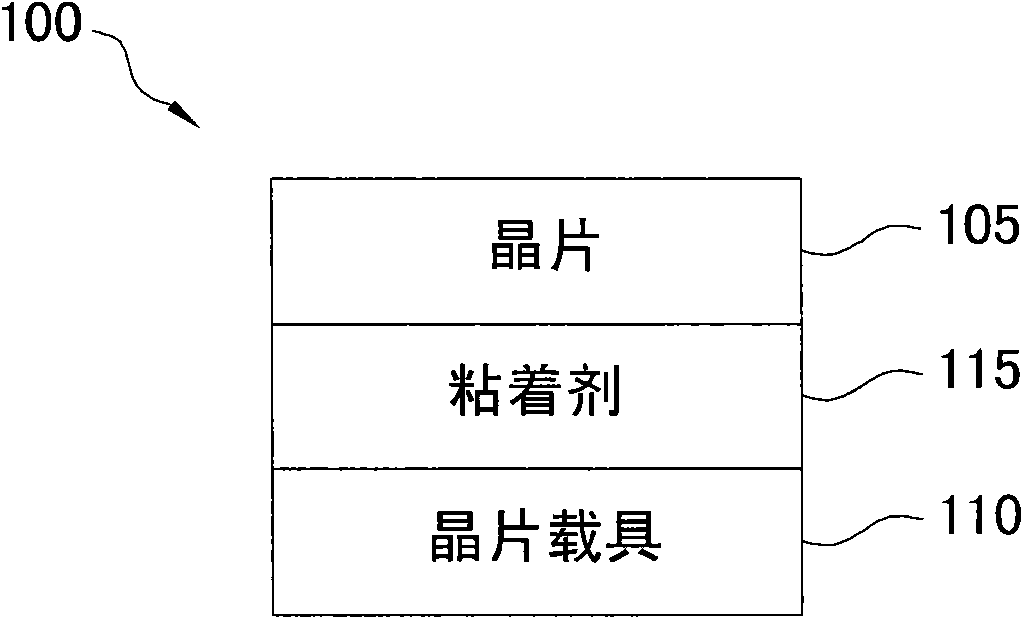

A chip carrier and chip technology, applied in the direction of electric solid-state devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of difficult removal of the chip 105, to save manufacturing costs, reduce costs and consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The embodiment of the present invention will describe the specific background technology, that is, the integrated circuit manufactured by the die-on-top technology. However, the present invention can also be applied to integrated circuits manufactured using other process technologies as long as the level of the wafers used to manufacture the integrated circuits needs to be maintained during the process.

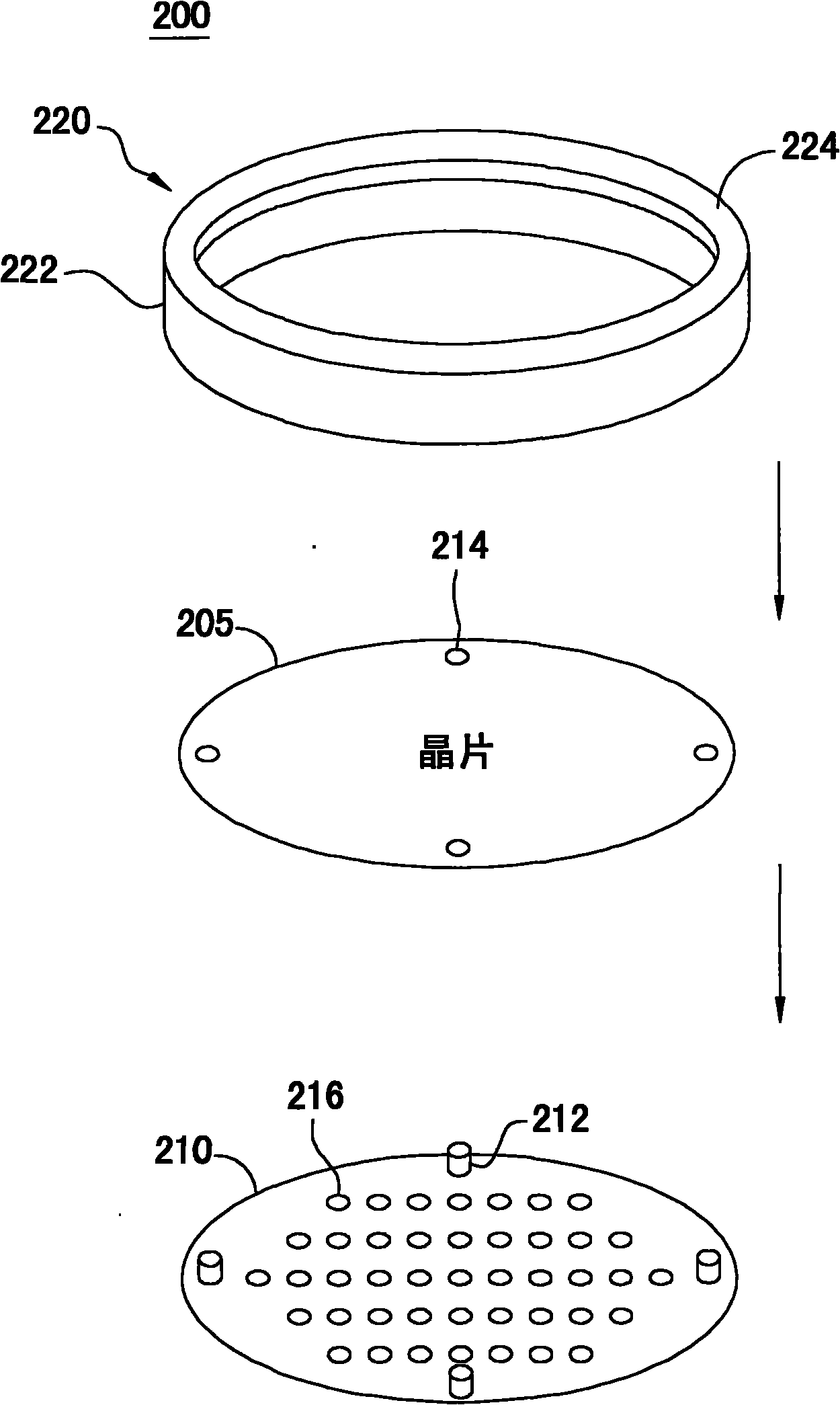

[0045] Figure 2a is an isometric view of a wafer holding system 200 for holding a wafer 205 for fabrication in accordance with an embodiment of the present invention. According to an embodiment of the present invention, when the integrated circuits are fabricated on the wafer 205, the wafer 205 can be placed on a wafer carrier 210, so that the handling of the wafer 205 can be simple and safe.

[0046]In order to make the alignment of the wafer 205 on the wafer carrier 210 more precise, the wafer carrier 210 may have a plurality of alignment posts (eg, alignment posts...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com