Structure and method for realizing concurrent reading and concurrent writing of IP of synchronous dual-port memory

A memory and dual-port technology, which is applied to the structure and field of parallel read and write of synchronous dual-port memory IP, which can solve the problems of non-portability and increased system instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The strategy proposed by the present invention has two key points: 1) selection and buffering of input signals; 2) selection of output data. These two key points are realized through input signal selection and cache strategy and output data selection strategy respectively.

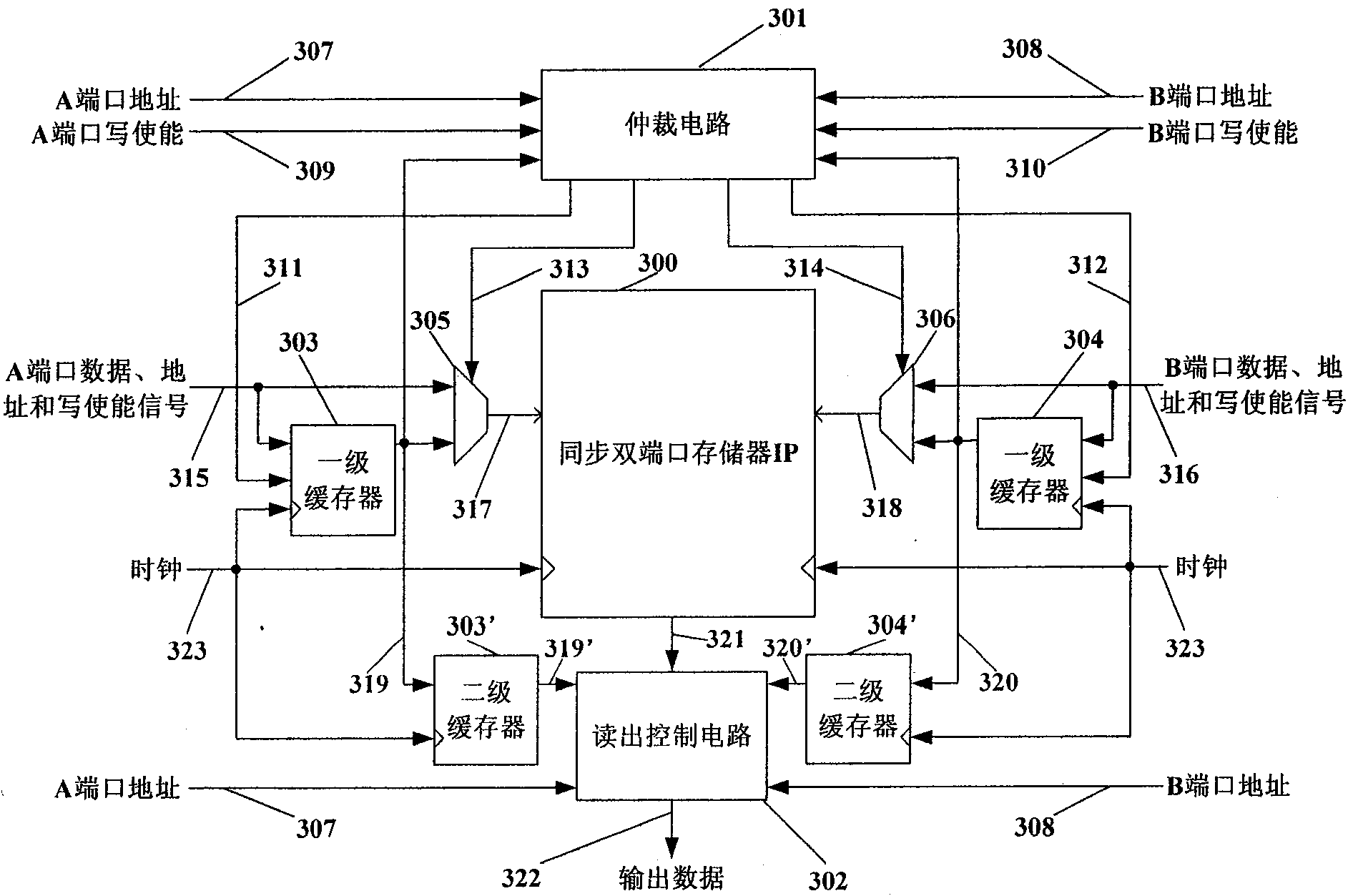

[0044] image 3 Shows the structure of the dual-port memory system in the present invention, which includes: synchronous dual-port memory IP 300, arbitration circuit 301, readout control circuit 302, primary buffers 303 and 304, secondary buffers 303' and 304' , and selectors 305 and 306.

[0045] Wherein, the arbitration circuit 301, the L1 registers 303 and 304, and the selectors 305 and 306 mainly complete as Figure 4 The input signal selection and buffering strategy shown. The L1 buffer 303 and the selector 305 correspond to the A port, and operate on the input signal of the A port; the L1 buffer 304 and the selector 306 correspond to the B port, and operate on the B port input signal. It s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com