Control logical circuit and successive approximation analog-to-digital converter

A technology for controlling logic circuits and circuits, applied in analog/digital conversion, code conversion, instruments, etc., can solve problems such as operation optimization without consideration of correlation, smaller setup and hold time margins, increased power consumption, etc., to avoid Timing check step, reduction of gate count, effects of saving area and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

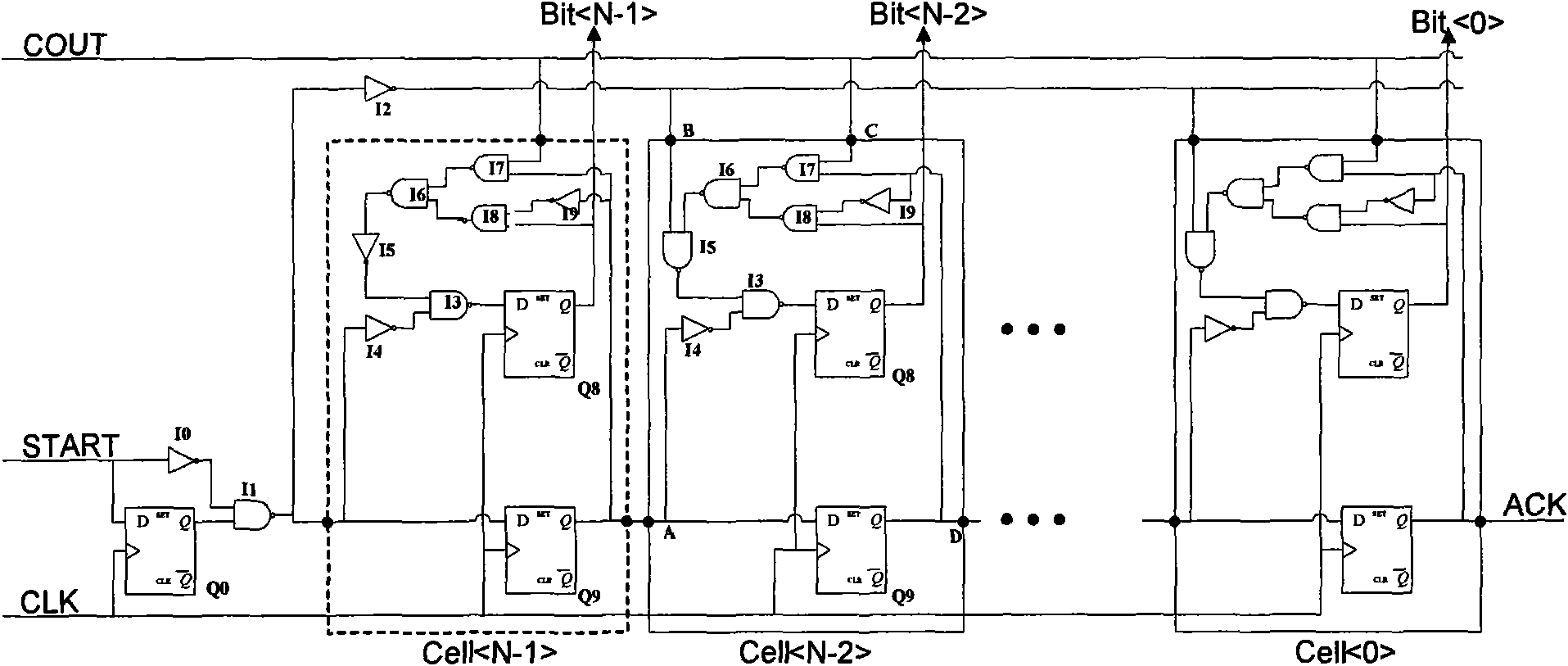

[0053] In order to make the above objectives, features and advantages of the present invention more obvious and understandable, the present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments.

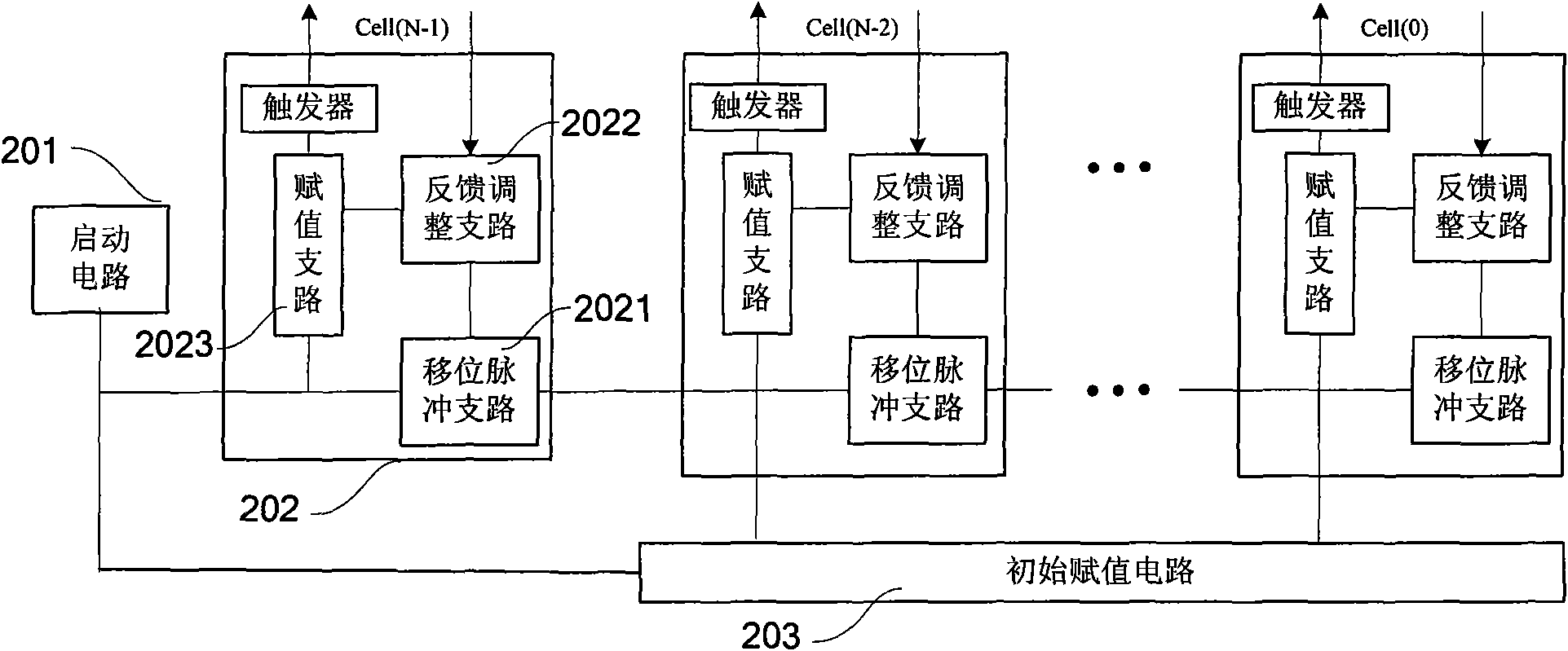

[0054] The core idea of the present invention is that the successive approximation mode and synchronous control logic are still adopted in the principle realization, but the simplified control logic and the simplified circuit are realized in the specific circuit structure to reduce the complexity of the overall circuit.

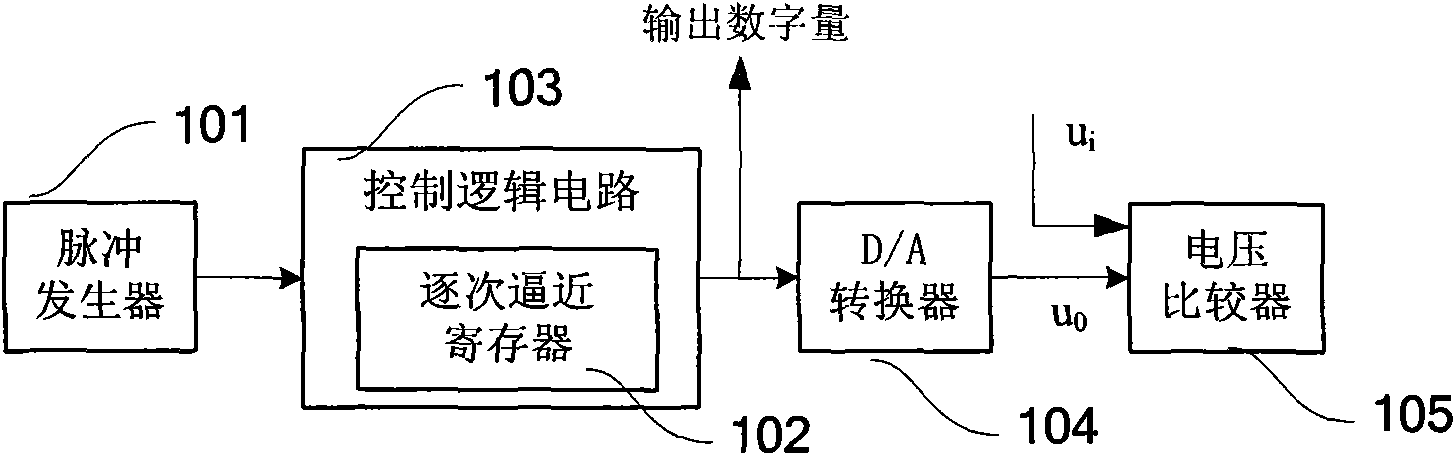

[0055] Reference figure 1 , Shows a structural block diagram of an embodiment of a successive approximation analog-to-digital converter of the present invention. It can specifically include:

[0056] The pulse generator 101 is used to generate a clock pulse signal and a start signal to start conversion;

[0057] The successive approximation register 102 is used to store the converted binary value of each d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com