Clock-synchronization digital phase-locking method and device

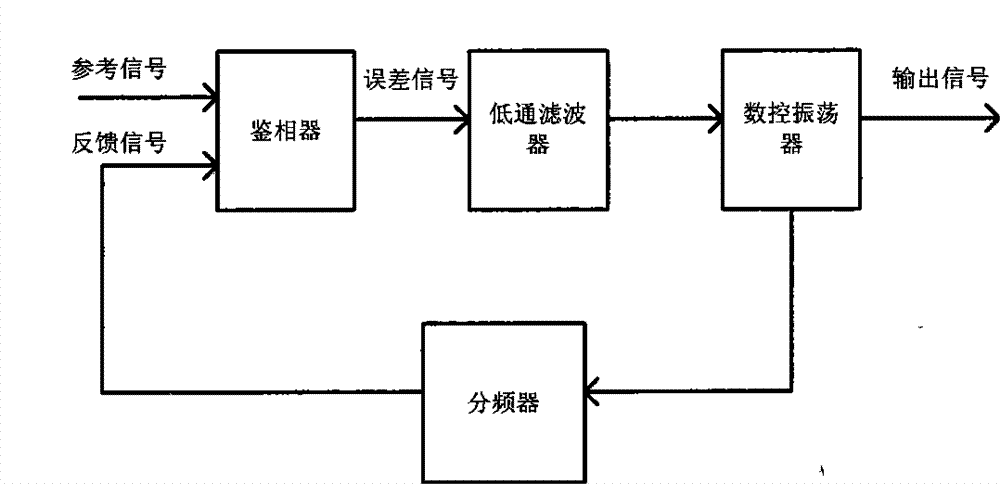

A digital phase-locking and clock synchronization technology, applied in the field of signal phase-locking, can solve the problems of increasing the locking time and reducing the sensitivity of the phase-locked loop, etc., and achieve the effect of fast phase-locking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described below with specific embodiments. Use the method and device described in the present invention to lock the falling edge of a signal with a frequency of 8KHz (the frame synchronization signal commonly used in communication systems), and output a T1 clock signal (1.533MHz) synchronized with the falling edge of the reference signal as an example Be explained.

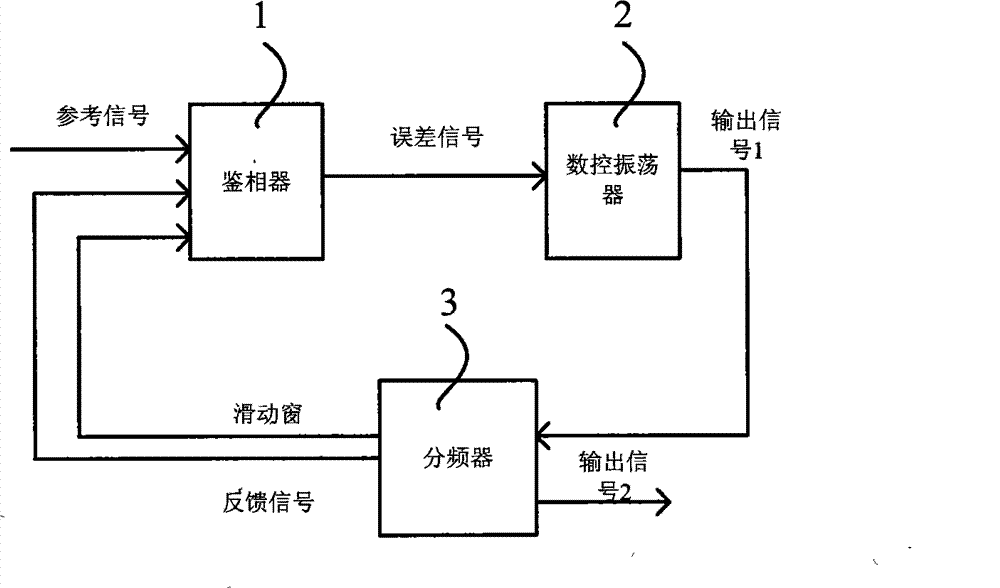

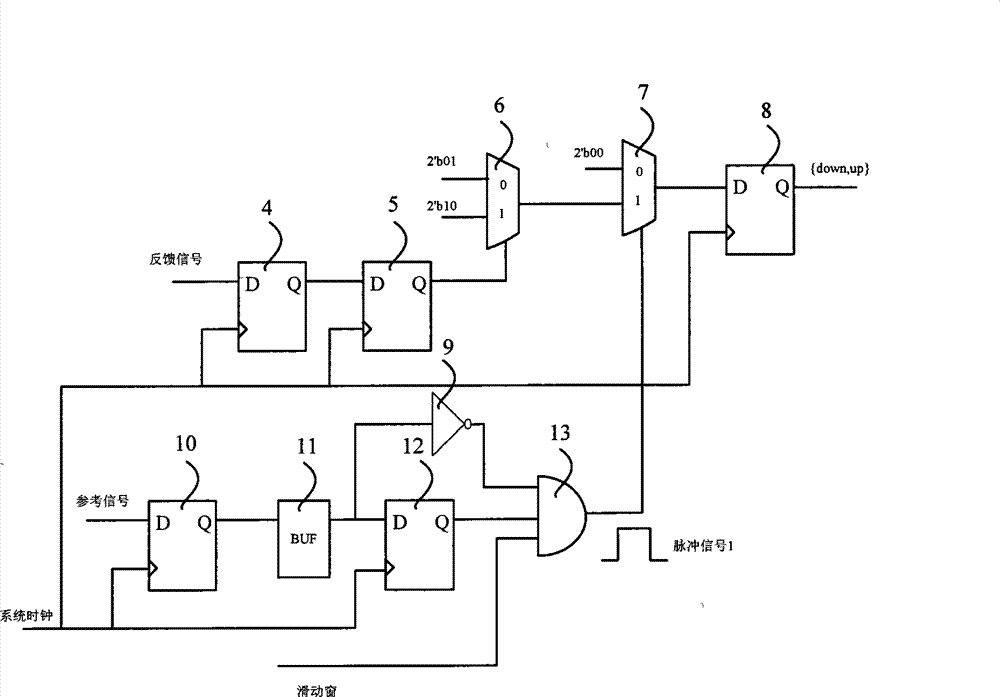

[0033] as attached figure 2 As shown, the digital phase-locked loop includes a phase detector 1, a digitally controlled oscillator 2 and a frequency divider 3. The phase detector 1 is used for phase comparison between the reference signal and the feedback signal, and generates an error signal in different regions of the sliding window according to the edges of the reference signal and the feedback signal. The numerically controlled oscillator 2 generates a corresponding phase-adjusted output signal 1 according to the error signal output by the phase detector 1 of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com