Thin film transistor (TFT) array substrate and manufacture method thereof

A technology for thin film transistors and array substrates, applied in the field of thin film transistor array substrates and their manufacturing, can solve the problem that the gate insulating layer cannot fully meet the design requirements, and achieves reduction in the number of photomasks, high stability, and improved resistance. delay-tolerant effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

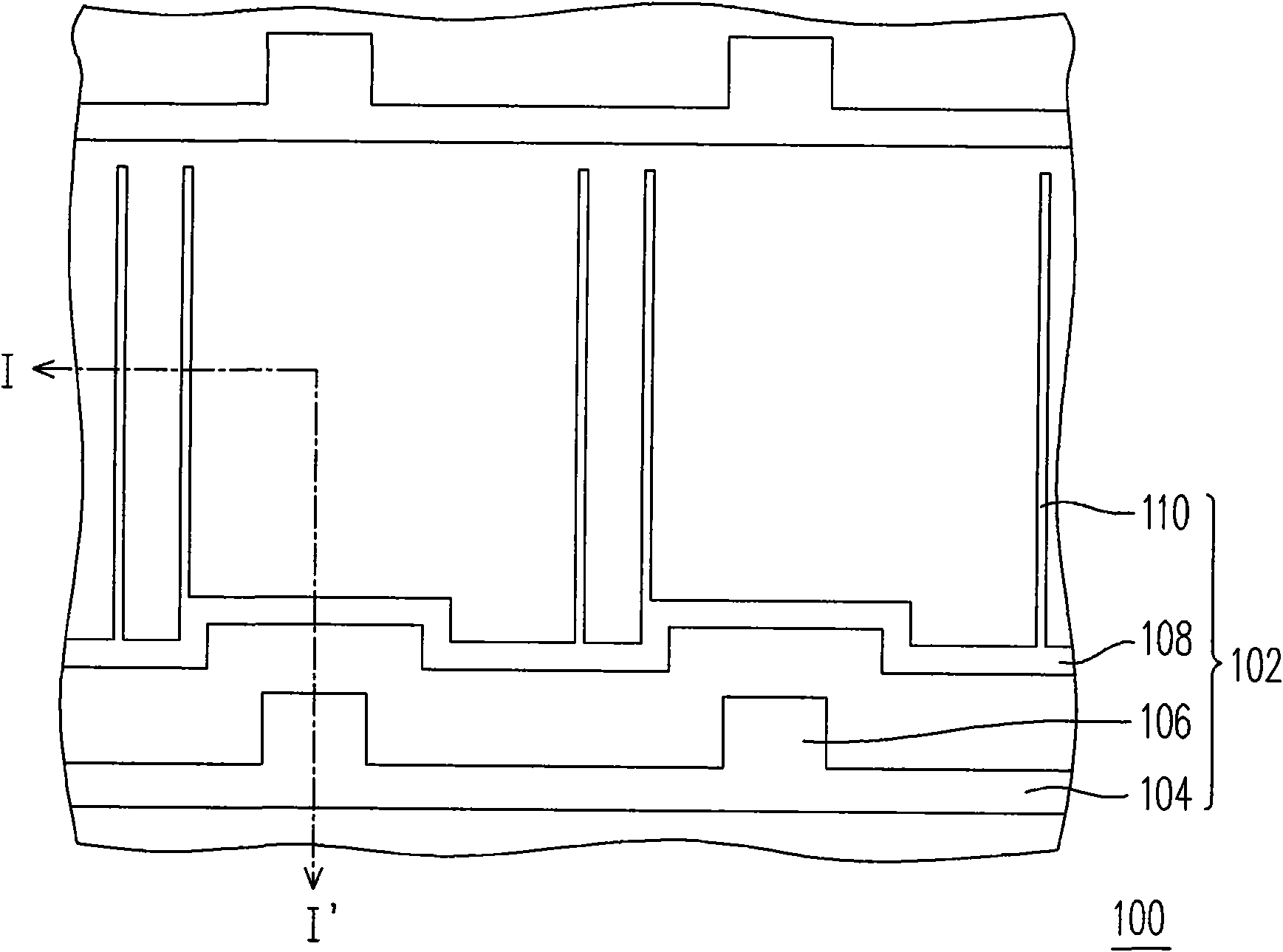

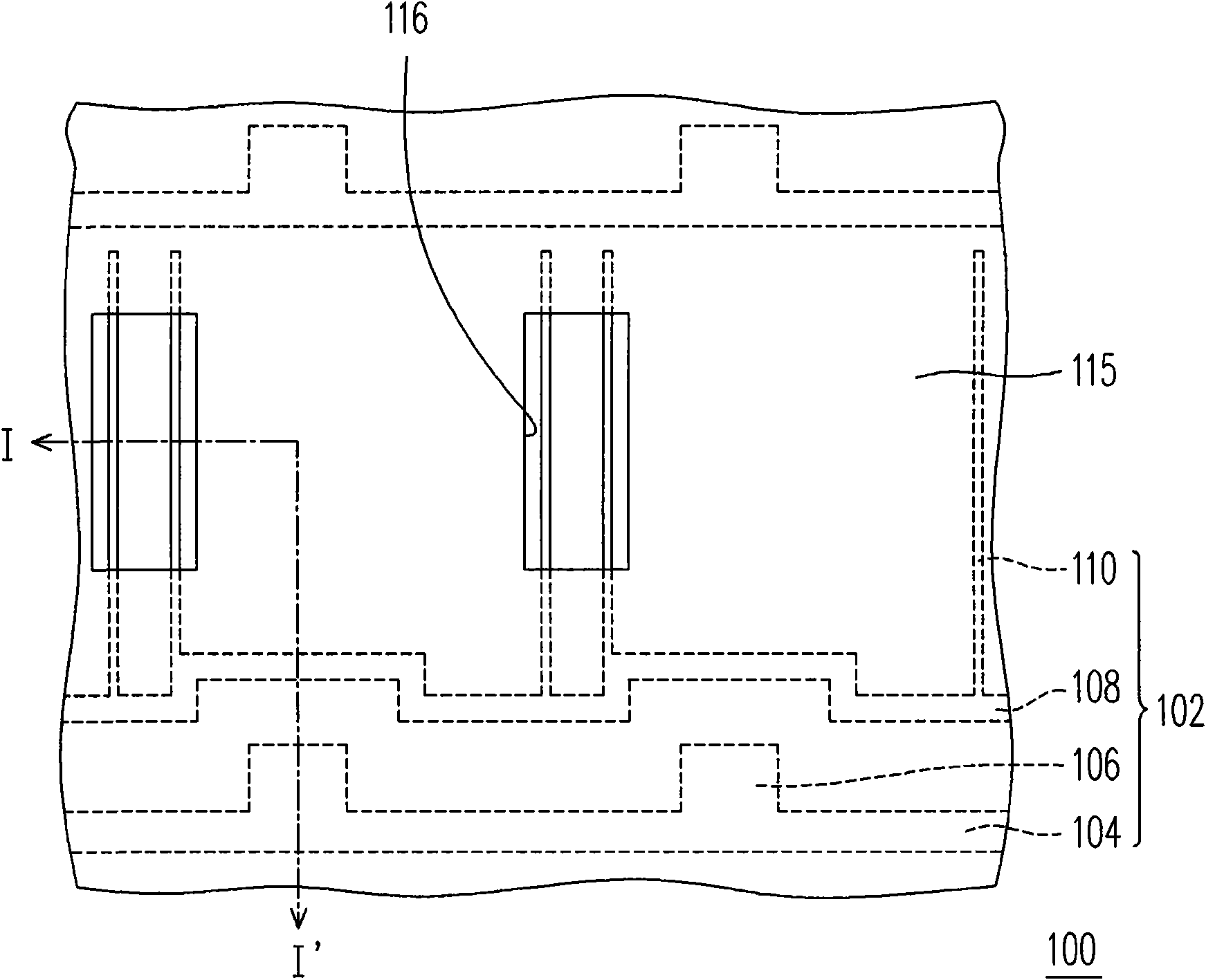

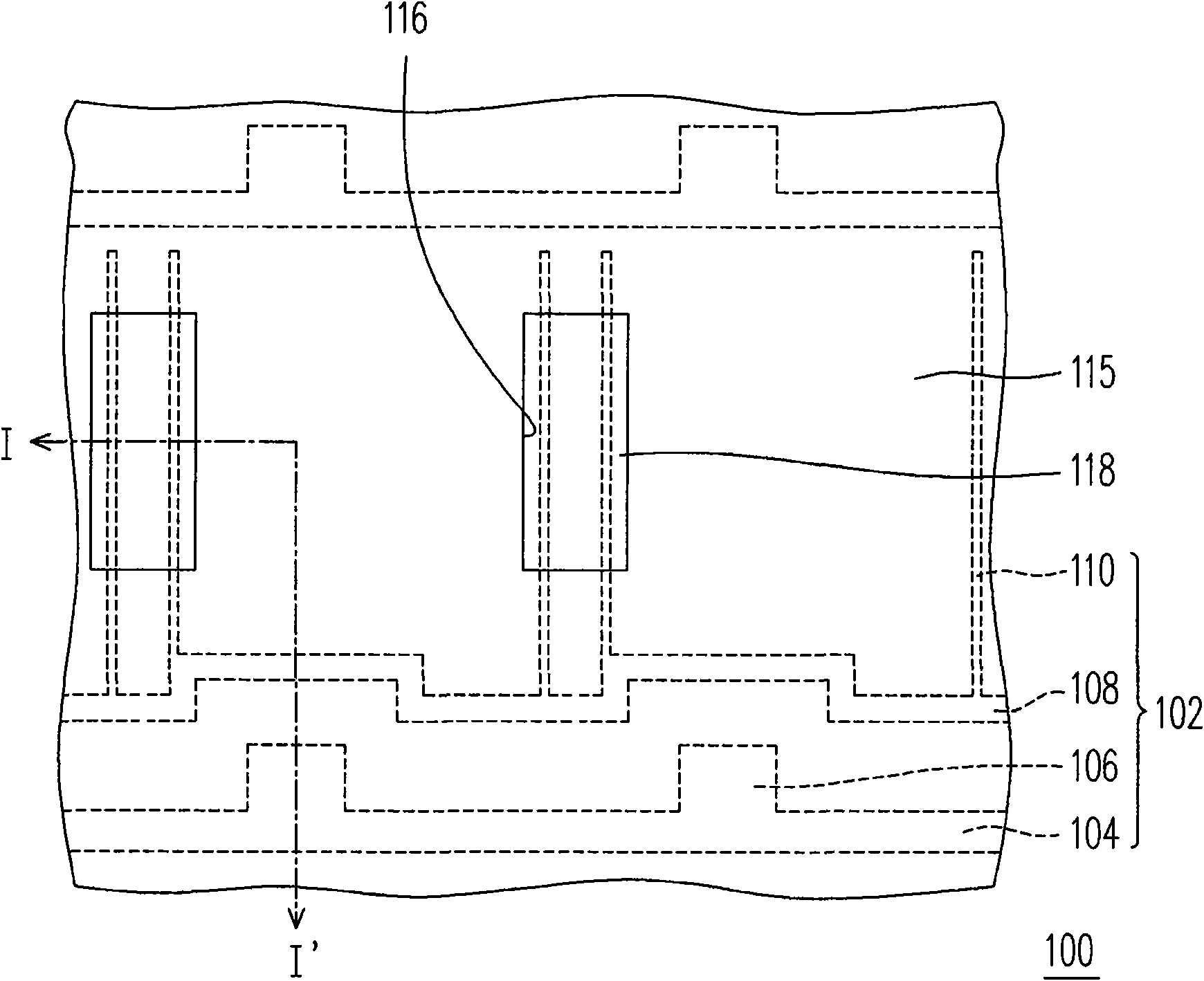

[0059] Figure 1A to Figure 1E It is a schematic top view of a thin film transistor array substrate according to an embodiment of the present invention. Figure 2A to Figure 2E respectively according to Figure 1A to Figure 1E The schematic cross-sectional view of the thin film transistor array substrate shown in the I-I' cross-section in . First, please also refer to Figure 1A and Figure 2A , forming a patterned conductive layer 102 on the substrate 100 . The material of the substrate 100 is, for example, glass, plastic or other suitable materials. The material of the patterned conductive layer 102 is, for example, metal. The patterned conductive layer 102 includes a scan line 104 and a gate 106 connected to the scan line 104 . In addition, the patterned conductive layer 102 also includes a common line 108 . A part of the common line 108 serves as a shielding layer 110 , for example, the shielding layer 110 can be parallel to the data line 124 .

[0060] Then, please ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com