Frame synchronous byte recognition system based on FPGA and recognition method

A recognition system and frame synchronization technology, applied in the direction of digital video signal modification, TV, electrical components, etc., can solve the problems of insufficient reliability and long detection time, so as to improve efficiency, occupy less resources, and reduce the time required for detection Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Below in conjunction with accompanying drawing and specific embodiment the present invention will be described in further detail:

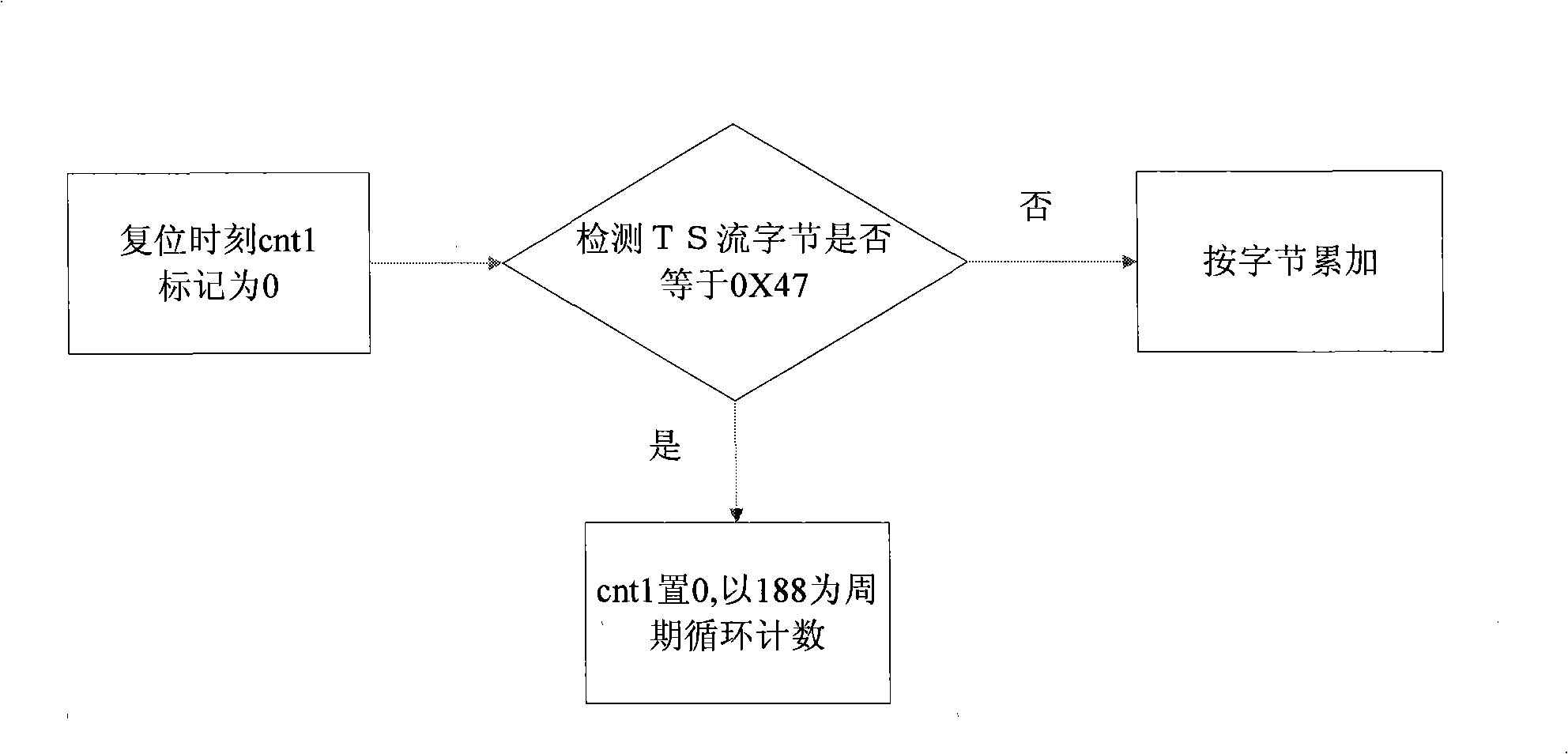

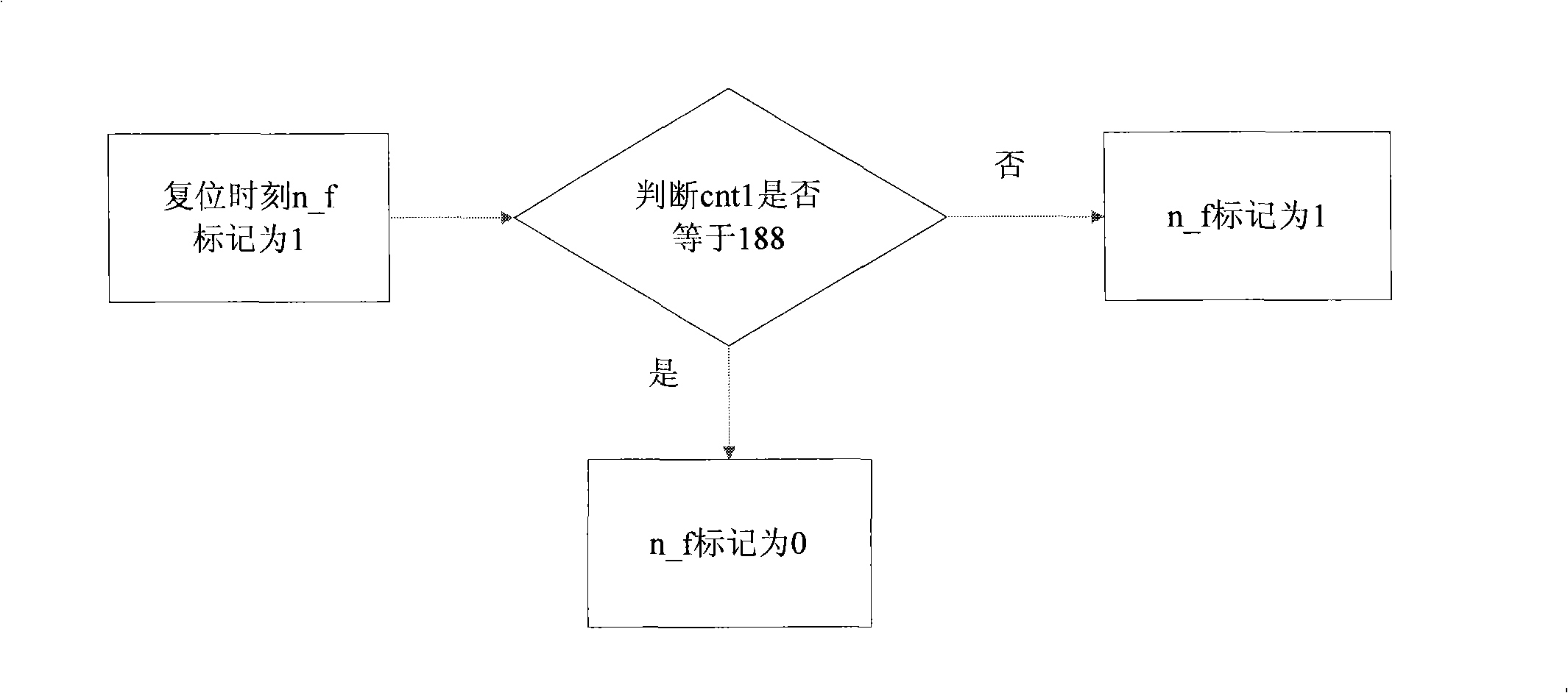

[0033] The present invention takes 188 bytes as an example to describe the FPGA-based frame synchronization byte recognition system and recognition method:

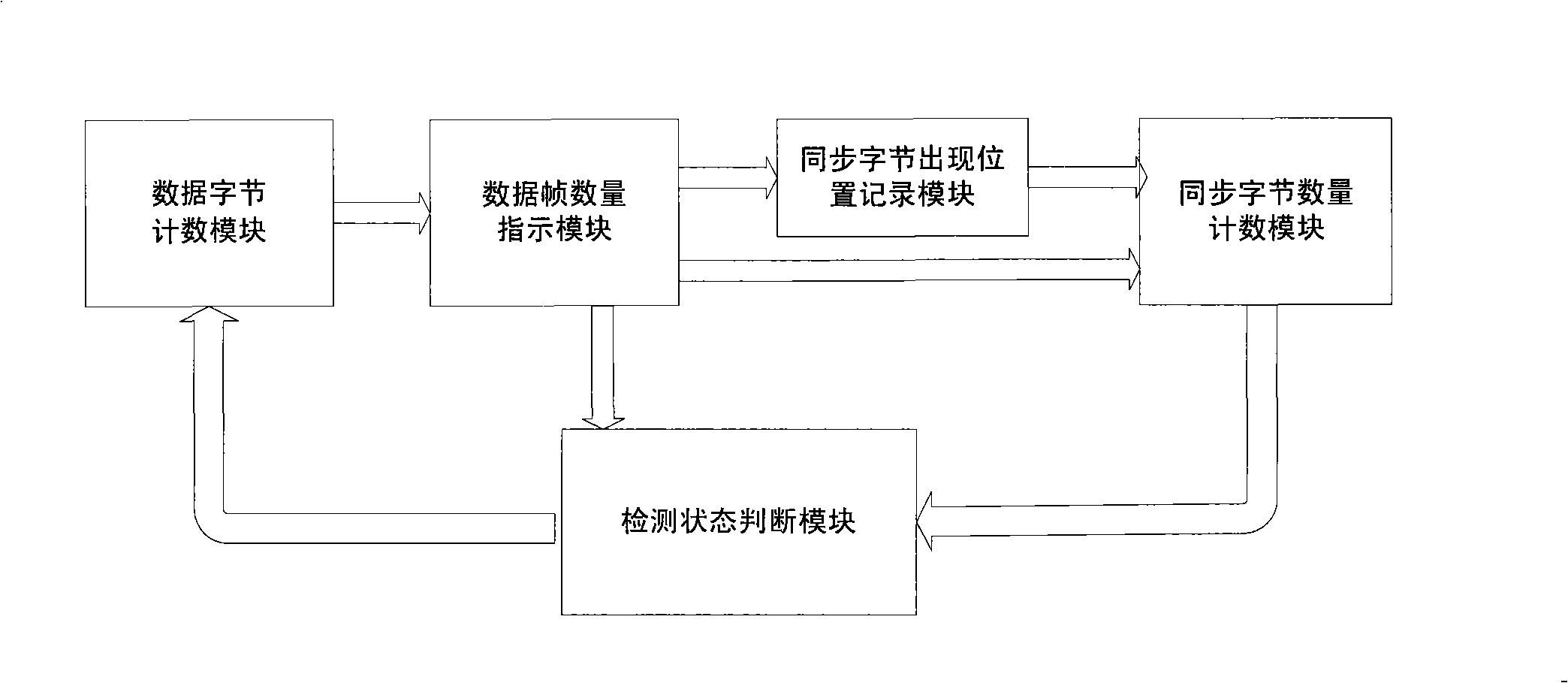

[0034] Such as figure 1 As shown, it is a simplified structural diagram of the FPGA-based frame synchronization byte recognition system of the present invention. As can be seen from the figure, the FPGA-based frame synchronization byte recognition system of the present invention includes a monitoring state judgment module, a data byte counting module, and a synchronization byte occurrence Position recording module, five modules of synchronous byte quantity counting module and data frame quantity indicating module, wherein the data byte counting module counts the data bytes of the current data frame of the TS stream, and records each byte in the current data frame The position within, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com