Three-dimensional stack chip structure with vertical electrical self-connection and manufacturing method thereof

A chip structure and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as high cost, complex process and time-consuming, and achieve low-cost effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

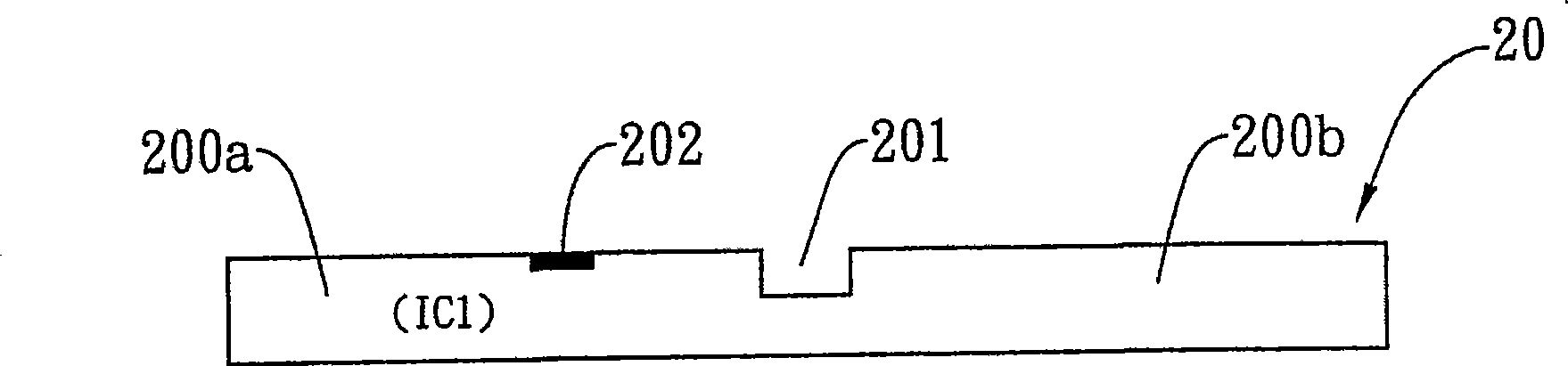

[0044] Figure 1A and Figure 1B It is a schematic diagram of the technology for forming electrical self-connection between metal pads 102 on a chip 10, which adopts an electroless plating process (electroless plating process) to deposit metal 104 on each metal pad 102, so that the deposited metal 104 grows isotropically, Furthermore, a metal bridge is formed between each metal pad 102 to form an electrical self-connection between each metal pad 102 . The present invention further applies this concept to the structure of three-dimensional stacked chips, and establishes vertical electrical conduction between three-dimensional stacked chips by a simple electroless plating process.

[0045] The three-dimensional stacked chip structure with vertical electrical self-connection of the present invention and its manufacturing method will be described in detail as follows through the following embodiments with accompanying drawings:

[0046] Figure 2A to Figure 2J It is a structura...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com