General-purpose test board and its use method

A test board, general-purpose technology, used in electronic circuit testing, measuring electricity, measuring devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

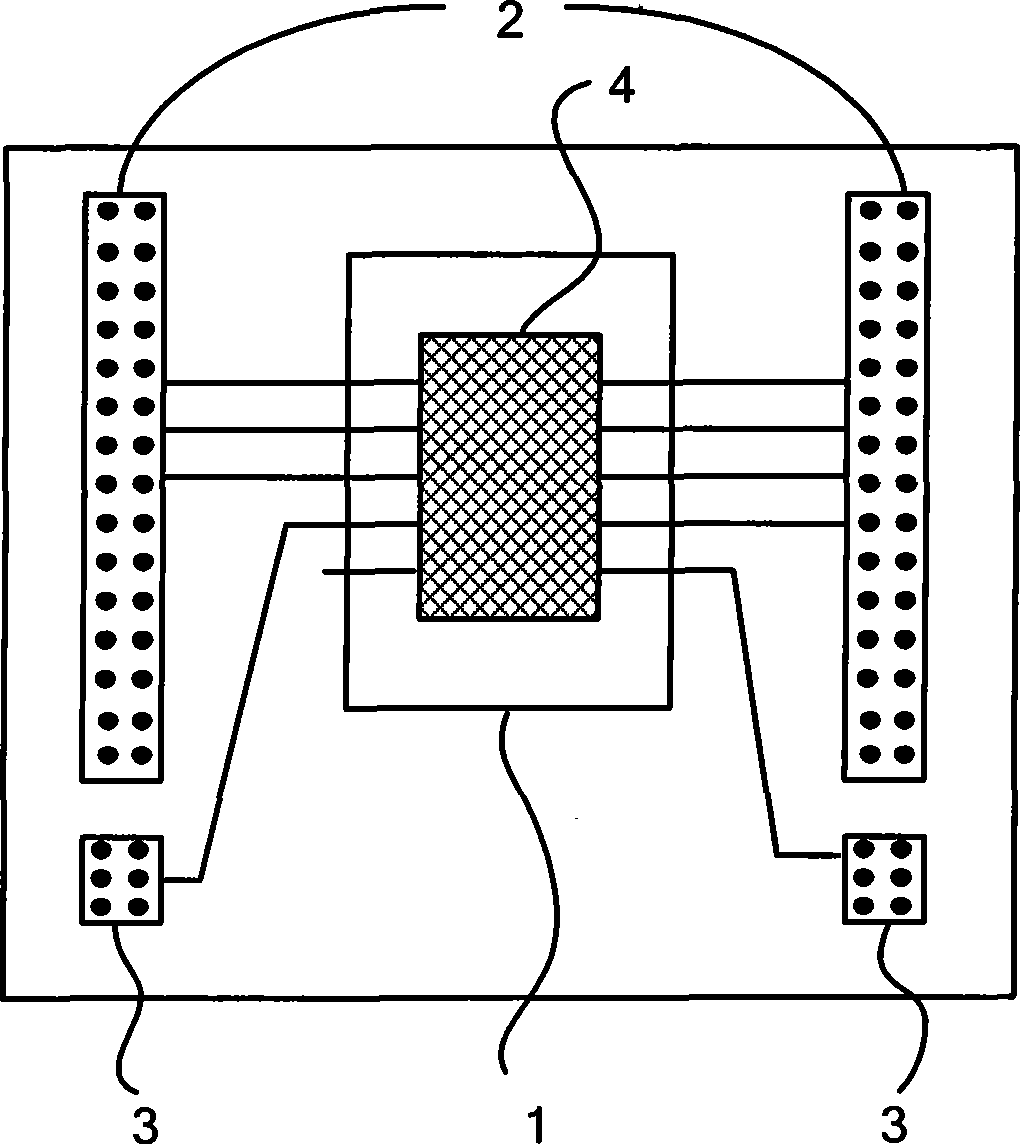

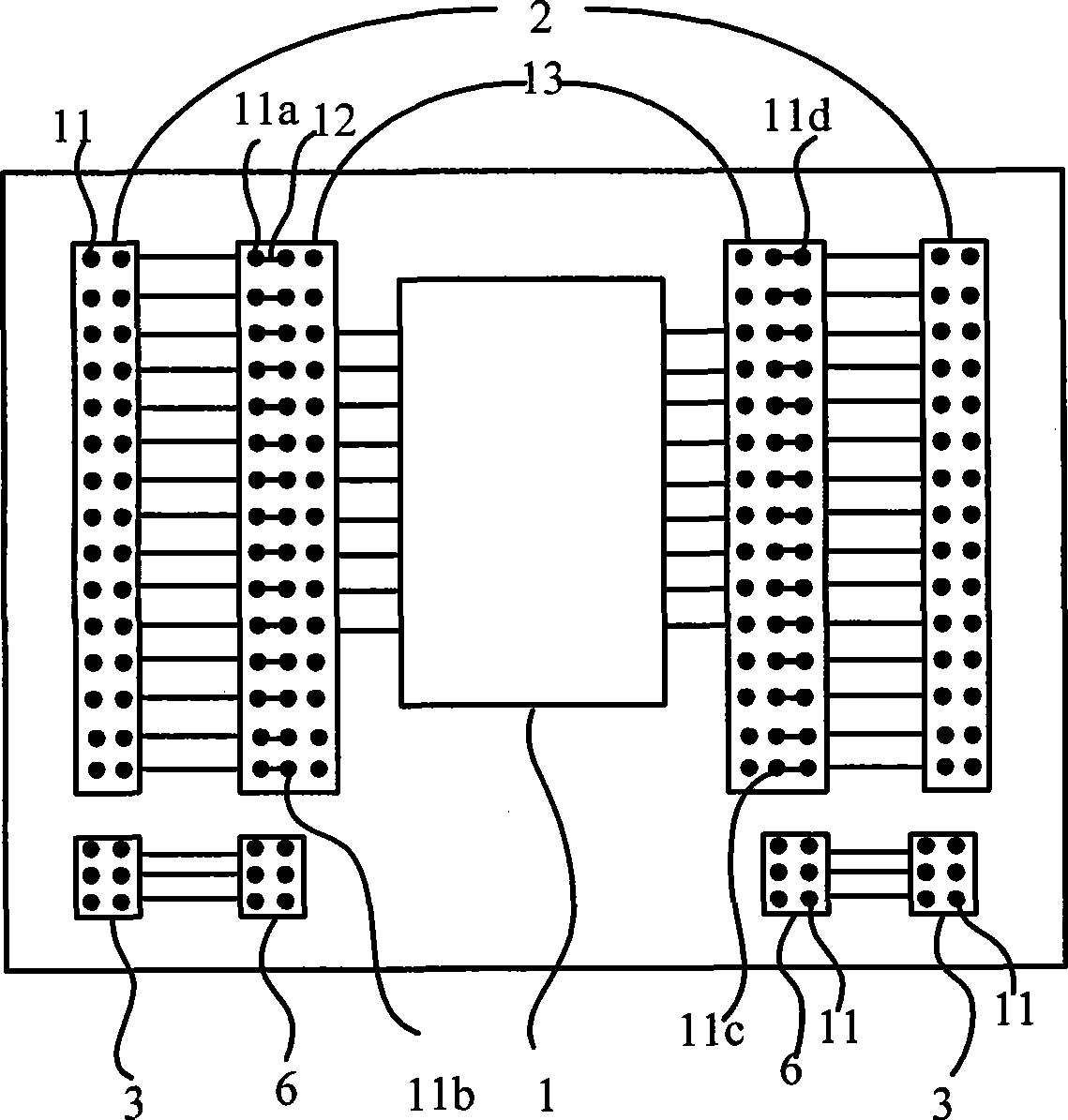

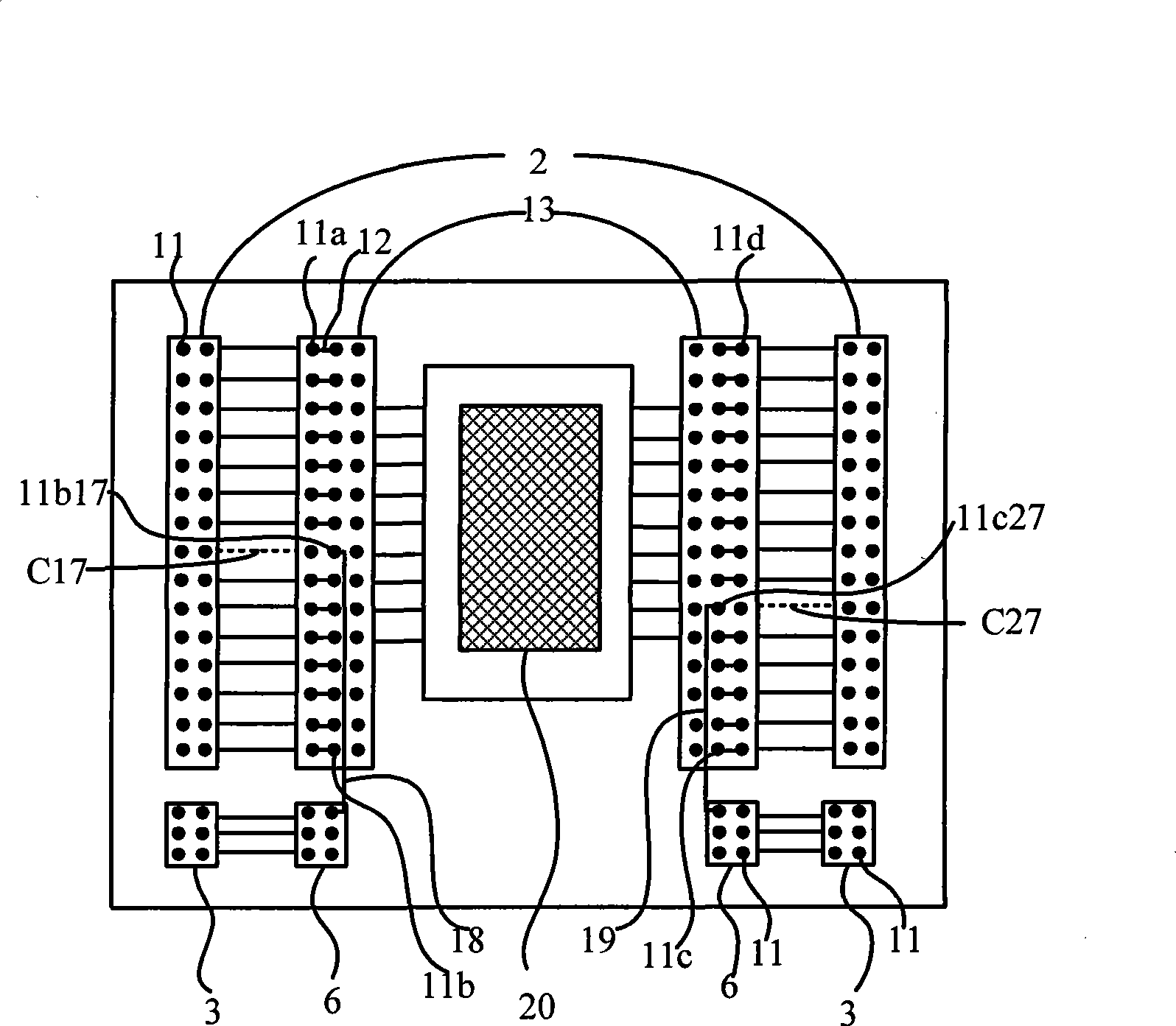

[0013] At present, DIP packaging is a commonly used packaging type in chip packaging. Take a general-purpose test board for testing DIP-packaged chips to be tested as an example. see figure 2 , this universal test board includes two connectors 2 with two columns of pins 11, two power connectors 3 with two columns of pins 11, chip sockets 1 with several pin slots and two with A buffer connector 13 with several rows of pins 11 and two power buffer connectors 6 with two rows of pins 11 . The buffer connector 13 is connected to the connector 2 and the chip socket 1 , and the power buffer connector 6 is connected to the power connector 3 . The pins of the power buffer connector 6 are connected to the pins of the power connector 3 .

[0014] The buffer connector 13 has three columns of pins and a group of connectors 12 (Jumper), wherein one column of pins 11a is connected to the connector 2, that is, one-to-one correspondingly connected with a column of pins of the connector 2; t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com