Method and apparatus for implementing hardware level verification

A hardware-level, verification board technology, applied in the field of system-on-chip, can solve the problems of low system operation speed, inability to truly realize SOC verification, and inability to provide effective SOC verification and IP verification at the same time, so as to achieve easy expansion, flexible and convenient implementation, cost reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

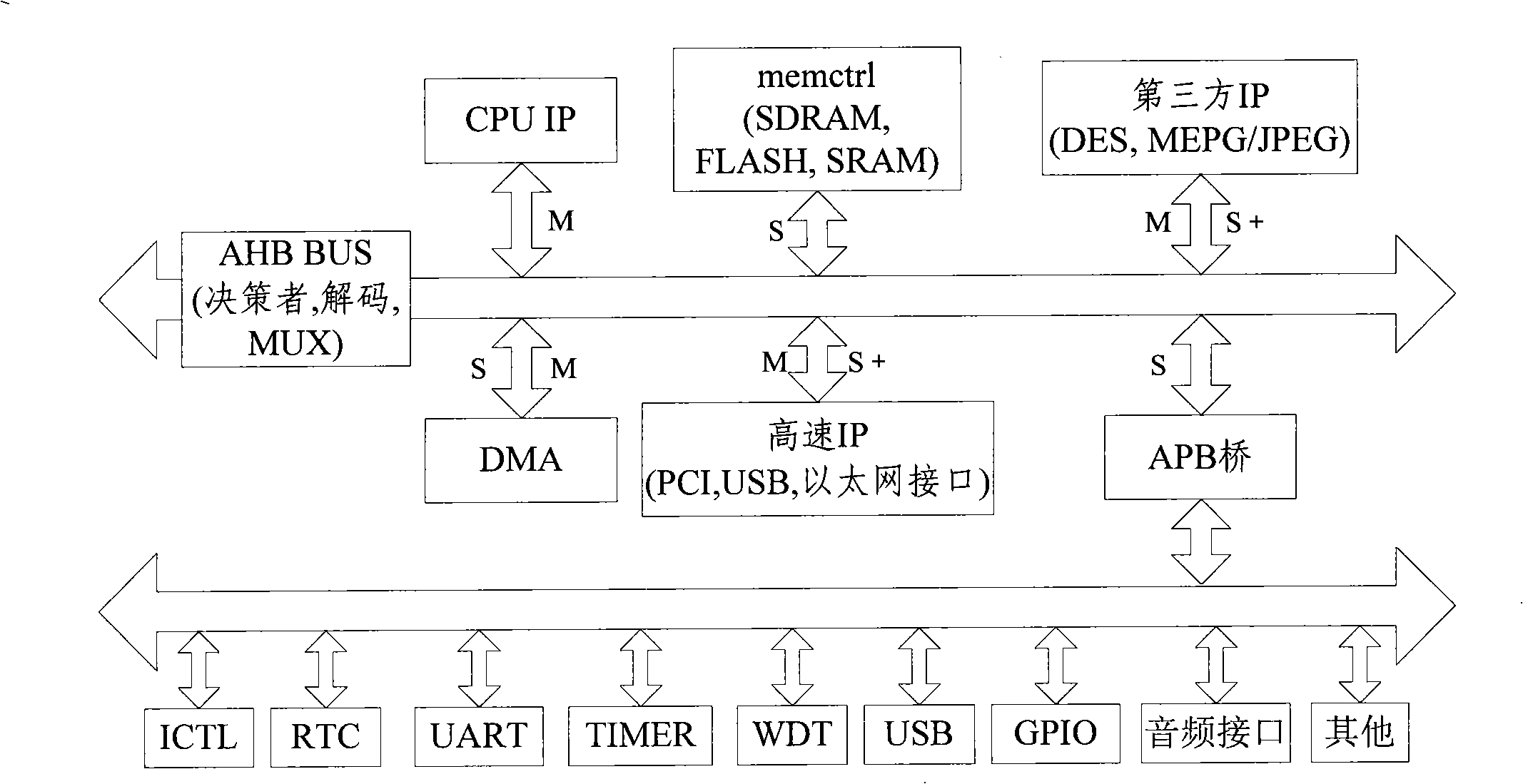

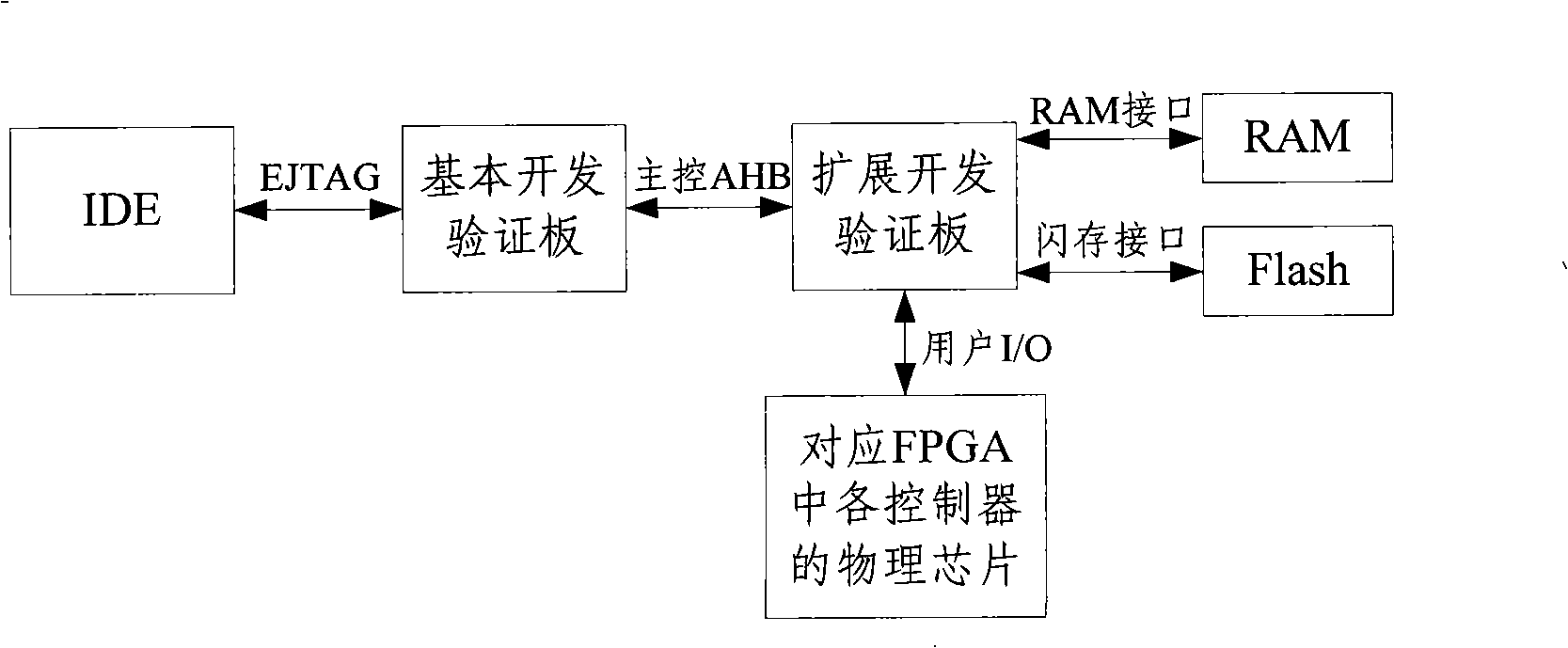

[0025] Since the on-chip bus used in the current SOC design is mainly the AMBA bus, the specific implementation of the present invention will be described in detail by taking the SOC based on the AMBA design as an example in the present invention. The basic structure of a SOC based on AMBA bus is as follows: figure 1 As shown, all modules are logic on the SOC, CPUIP and some high-speed interfaces are connected through the Advanced High-performance Bus (AHB, Advanced High-performance Bus) of the AMBA bus, and other low-speed interfaces are connected to the Advanced Peripheral Bus (APB) of the AMBA bus , Advanced Peripheral Bus), and connected to the AHB bus through the APB bridge.

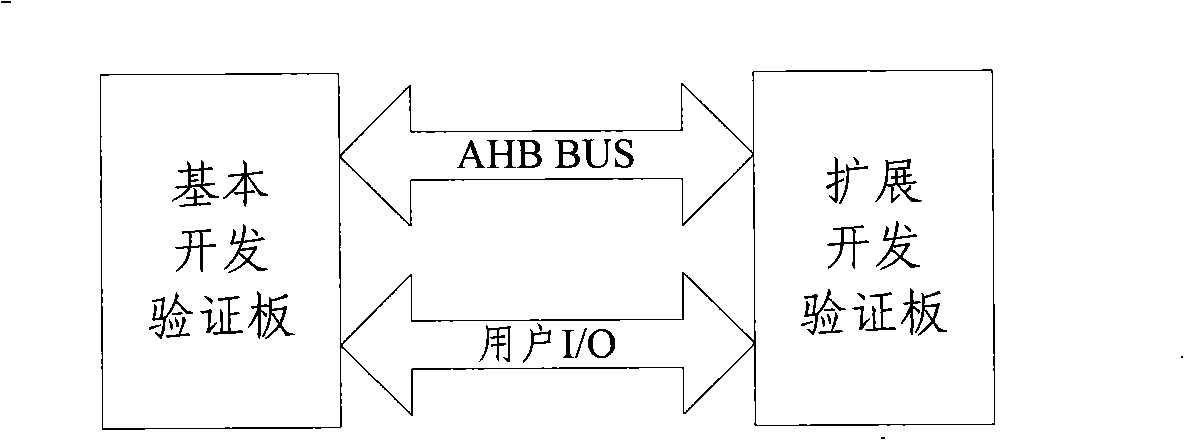

[0026] figure 2 It is a schematic diagram of the device structure for realizing SOC verification and IP verification in the present invention, such as figure 2 As shown, the device adopts the structure of basic development verification board + extended development verification board. Among them...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com