Method for forming elementary cell and crystal round with epitaxial slice

A technology of epitaxial wafers and cells, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem of large source-drain on-resistance, and achieve the effect of reducing source-drain on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

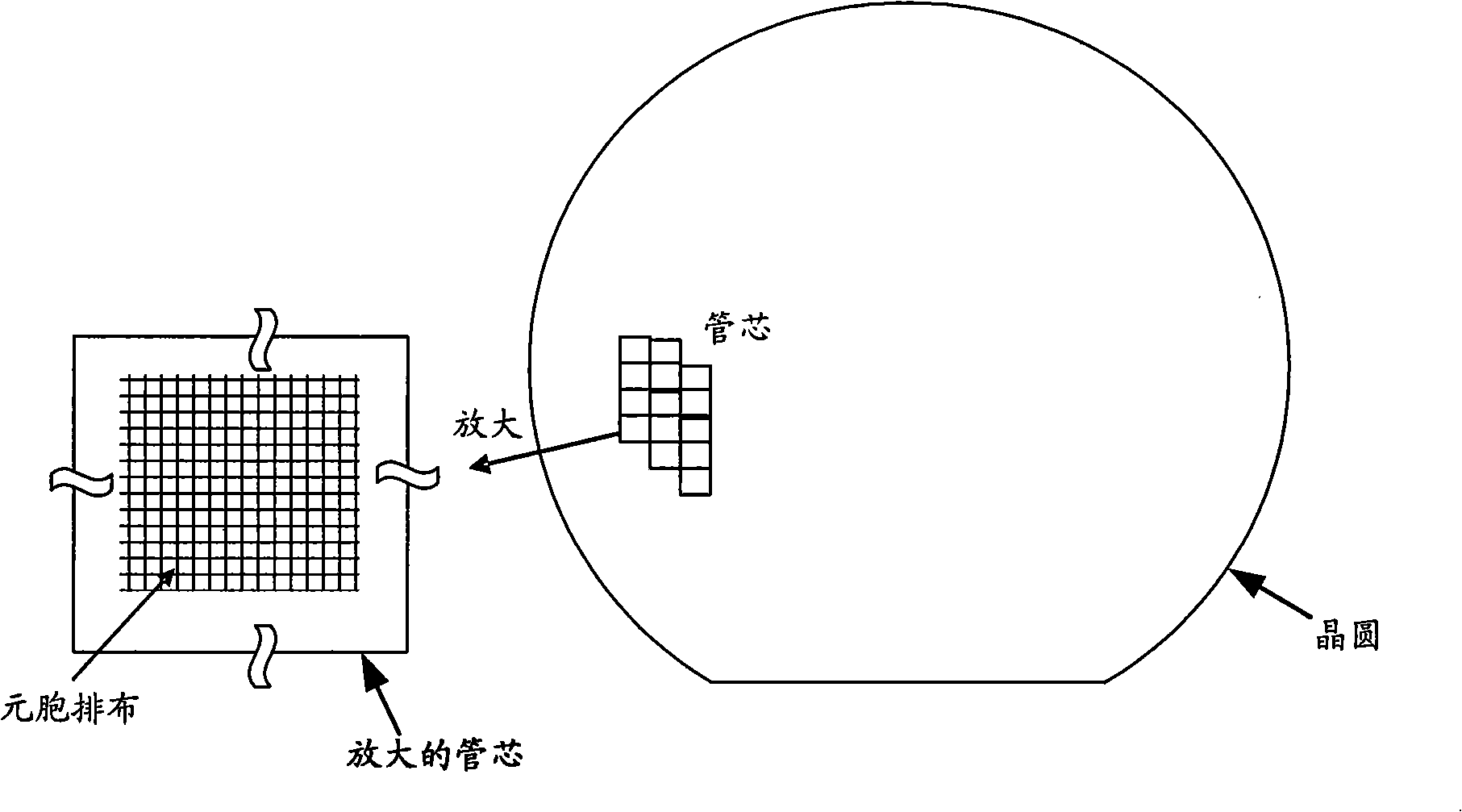

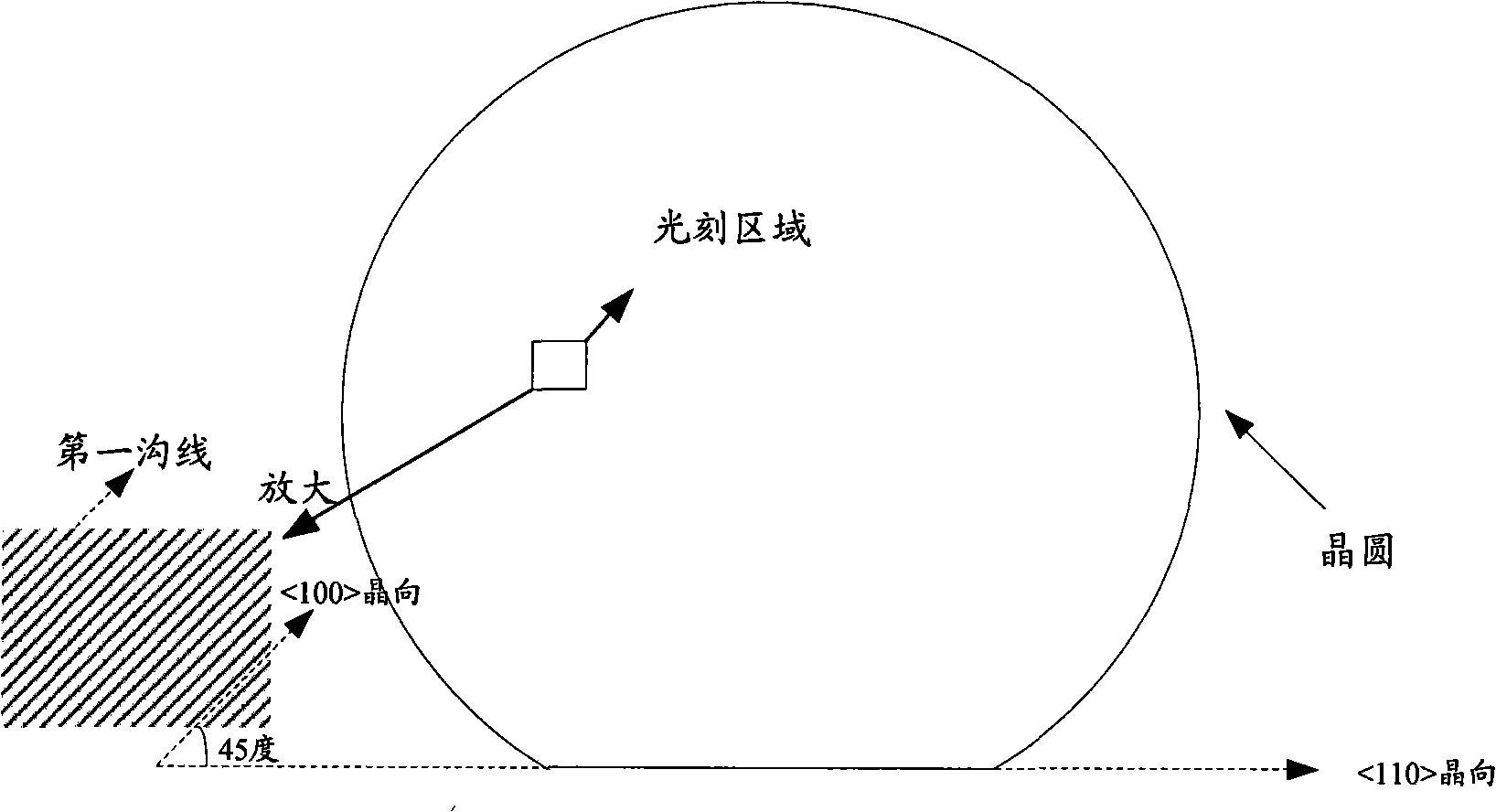

[0017] Embodiments of the present invention provide a method for forming cells and a wafer with epitaxial wafers. Utilize the method of the present invention to print on the surface of the epitaxial wafer in which the main flat side is located in the crystal direction, there are two opposite sides forming an angle of 45 degrees with the crystal direction. This cell unit The source-drain on-resistance on the area is smaller than the source-drain on-resistance of the square cell whose bottom side is parallel to the main flat edge of the epitaxial wafer, thereby reducing the source-drain on-resistance in the effective die area of the semiconductor device and improving the semiconductor performance. The performance of devices (such as DMOS devices, IGBT devices).

[0018] refer to figure 2 As shown, the method for forming cells on an epitaxial wafer includes the following steps:

[0019] S201. On the surface of the epitaxial wafer located in the crystal direction on the ma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com