Memory with retargetable memory cell redundancy

A technology of memory cells and memory arrays, used in static memory, instruments, etc., to solve problems such as programming time constraints

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

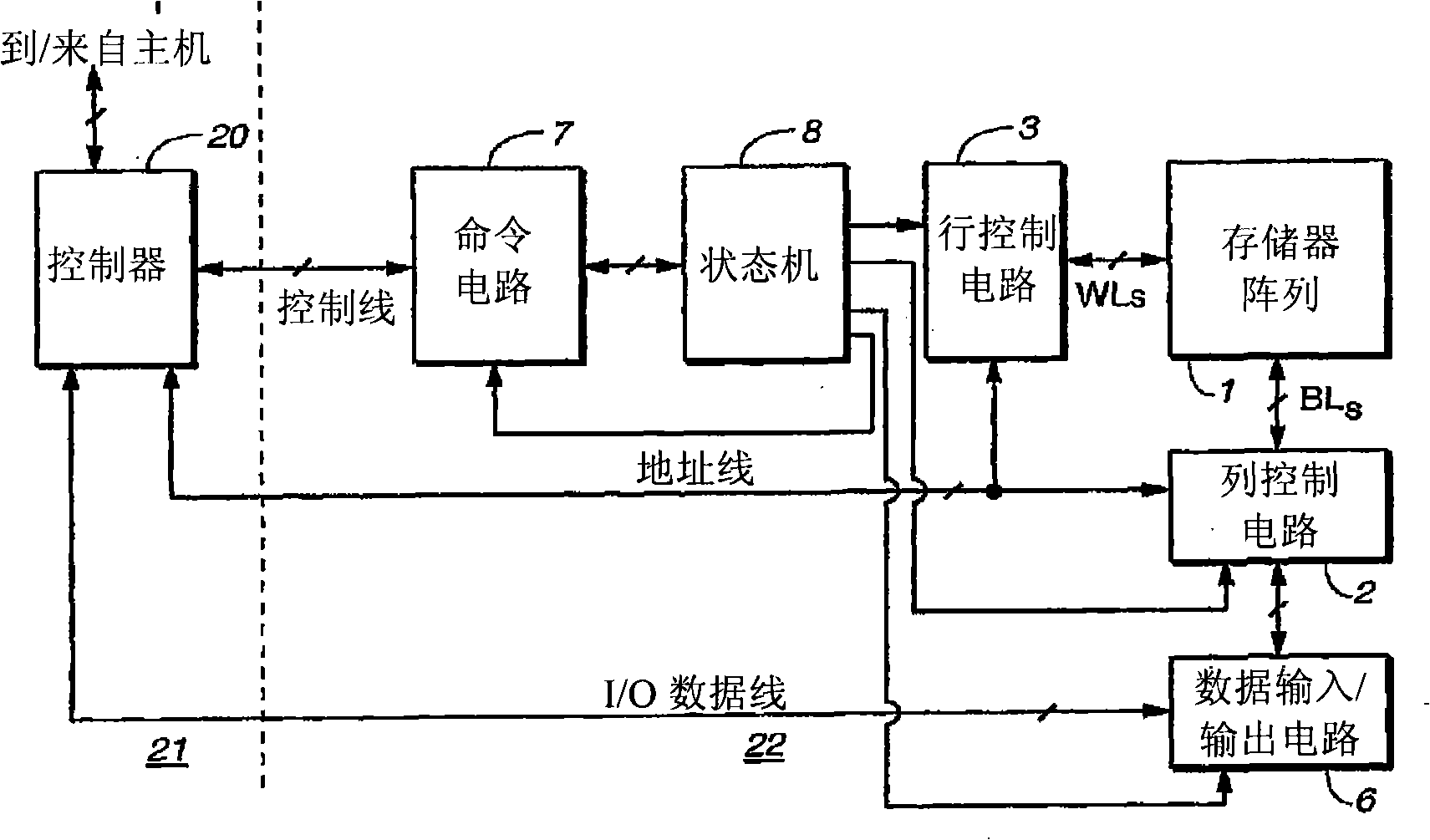

[0036] image 3 A memory system 330 is shown incorporating aspects of the invention. Memory system 330 is connected to and communicates with a host (not shown). This communication between the host and the memory system is typically performed through a standard interface. In some instances, a memory system (eg, memory system 330 ) is part of a removable memory card with a standard interface, so it can be connected to a wide variety of hosts according to standards such as those previously described. In an alternative arrangement, a memory system (eg, memory system 330 ) may be embedded in the host system, so it may be permanently connected to the host system.

[0037] The memory system 330 includes a controller 20 that controls the operation of the memory array 1 in response to commands received from the host. Controller 20 may contain a microprocessor, RAM, flash, buffers, registers, error correction code (ECC) circuits, and other circuits for managing memory system 330 . Wh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com