Assembly line a/d converter and method for eliminating sampling-hold circuit

A sample-and-hold circuit, analog-to-digital converter technology, applied in analog-to-digital conversion, code conversion, instruments, etc., can solve problems such as low sampling rate, and achieve the effect of improving tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

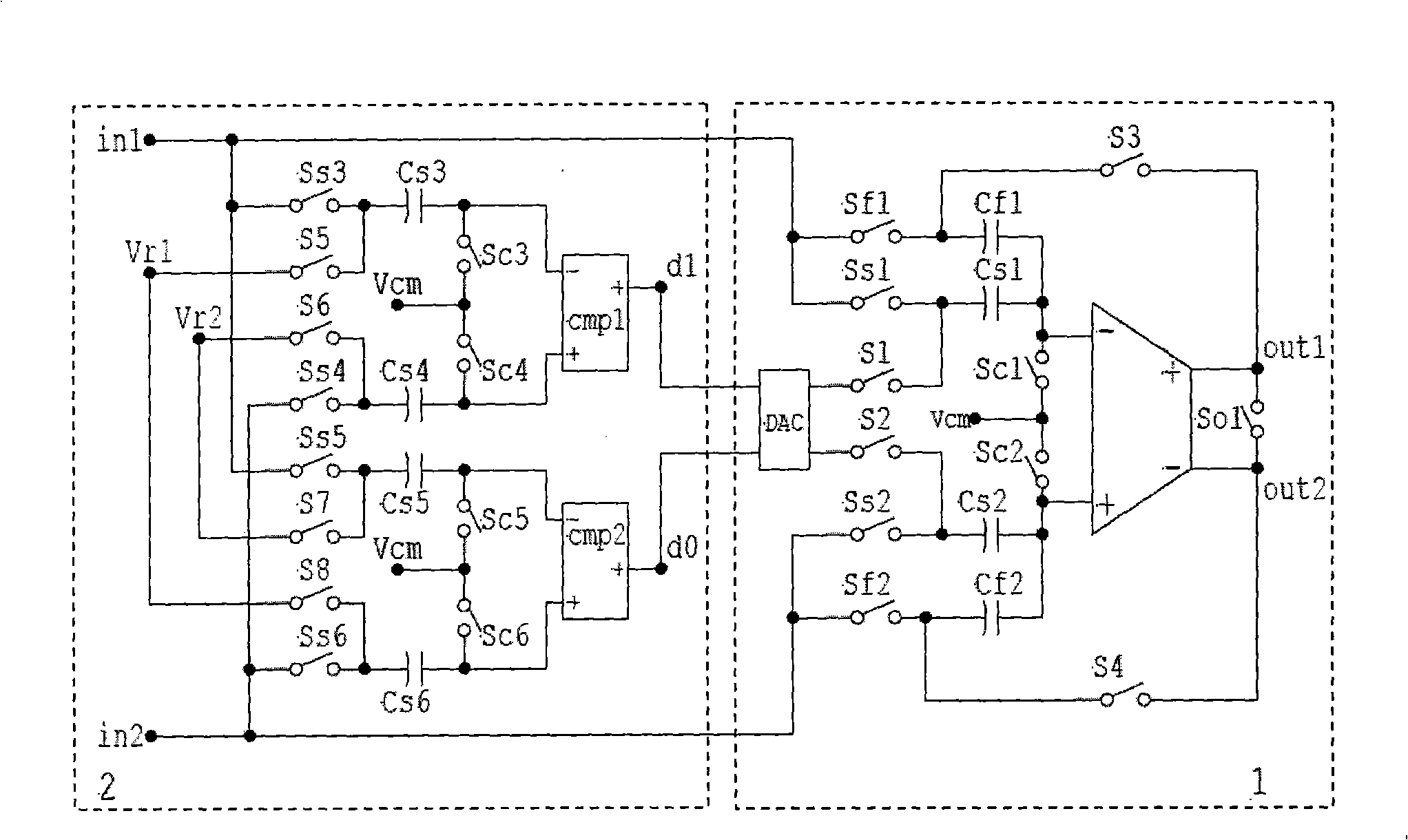

[0032] The invention provides a pipelined analog-to-digital converter which eliminates the sampling and holding circuit. The first-stage MDAC in the pipelined analog-to-digital converter adopts a 1.5-bit structure, so that the error correction range of the first-stage comparator is relatively large.

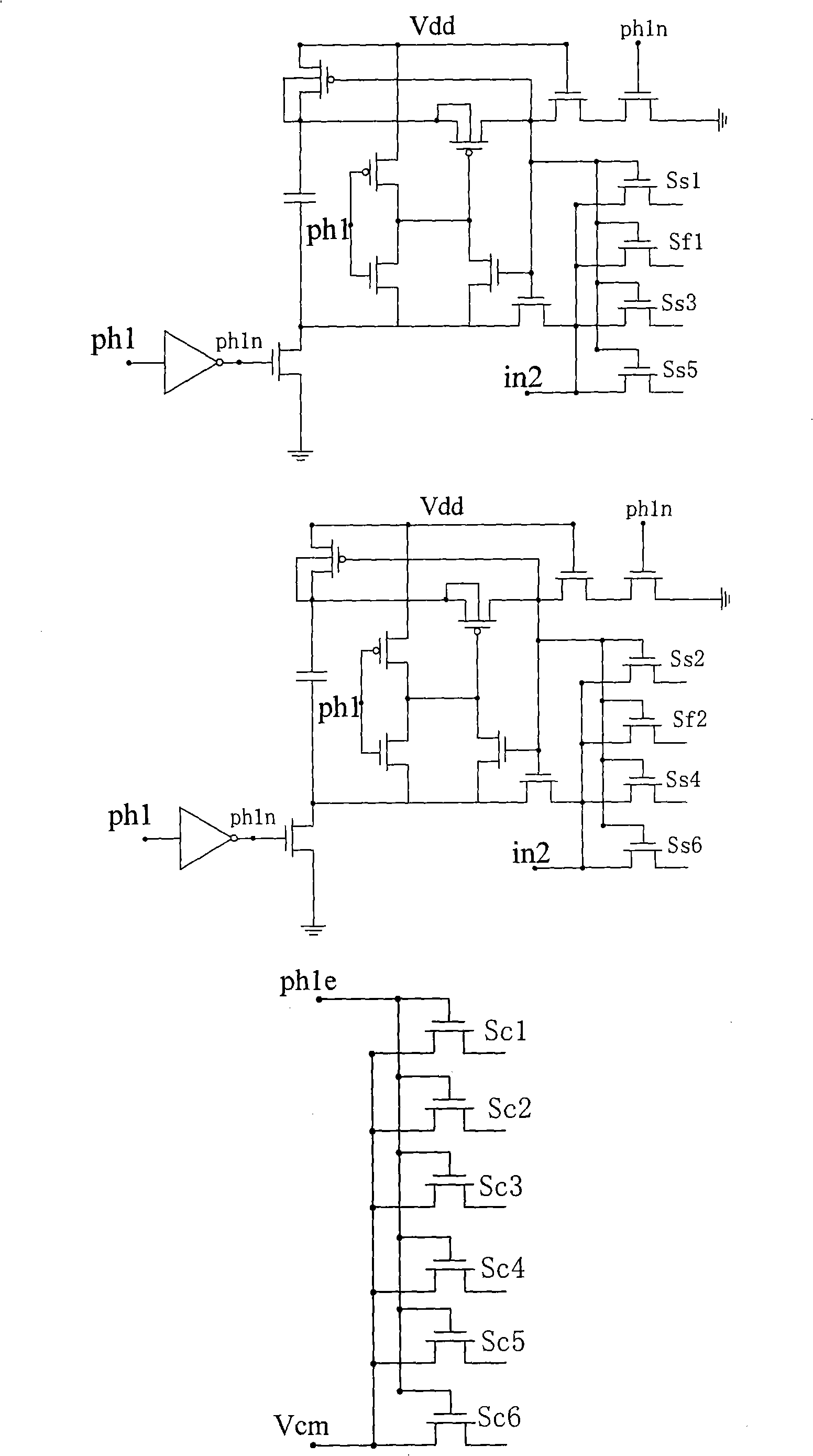

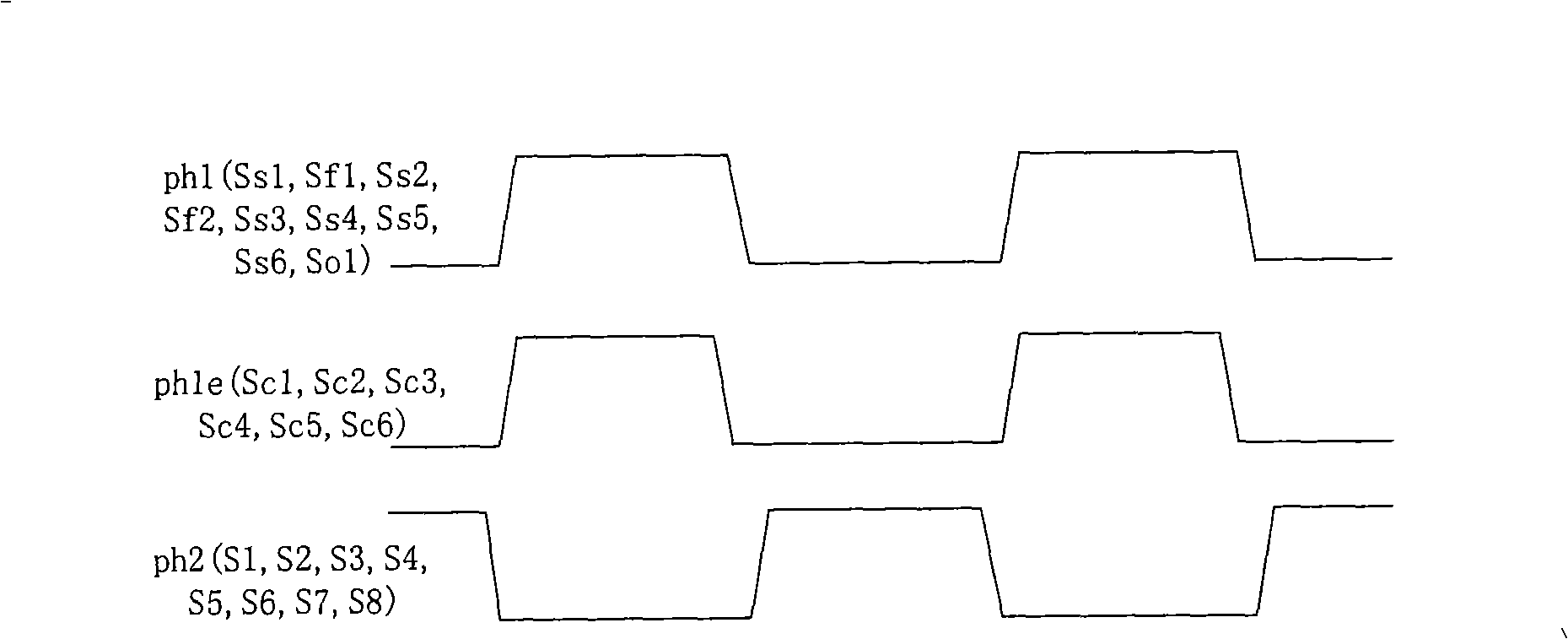

[0033]Further, the switches related to sampling in the first-stage MDAC circuit include Sc1, Sc2, Ss1, Ss2, Sf1, Sf2, and the switches related to sampling in the first-stage SUBADC include Sc3, Sc4, Sc5, Sc6, Ss3, Ss4, Ss5, Ss6, the pipeline analog-to-digital converter further uses the same clock signal ph1e to control Sc1, Sc2, Sc3, Sc4, Sc5 and Sc6, and uses the same clock signal ph1 to control Ss1, Ss2, Sf1, Sf2, Ss3, Ss4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com