Semiconductor isolation structure and forming method thereof

An isolation structure and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problem that the manufacturing process isolation structure and semiconductor substrate affect device performance, the transistor loses the switching current control function, and the power consumption of the transistor Problems such as penetration through the layers can achieve the effects of easy control of the injection process, avoiding complex forming processes, and good isolation performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

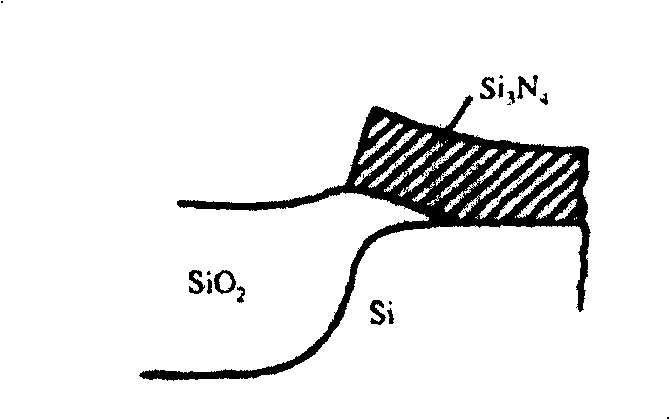

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

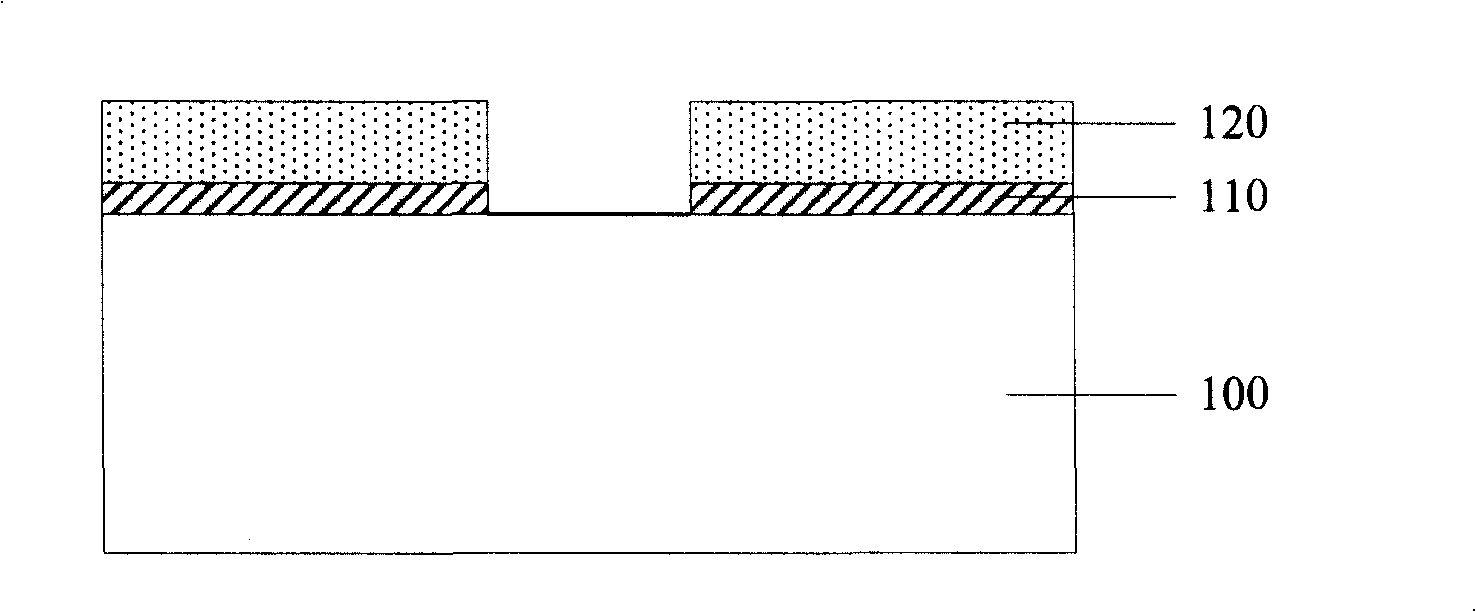

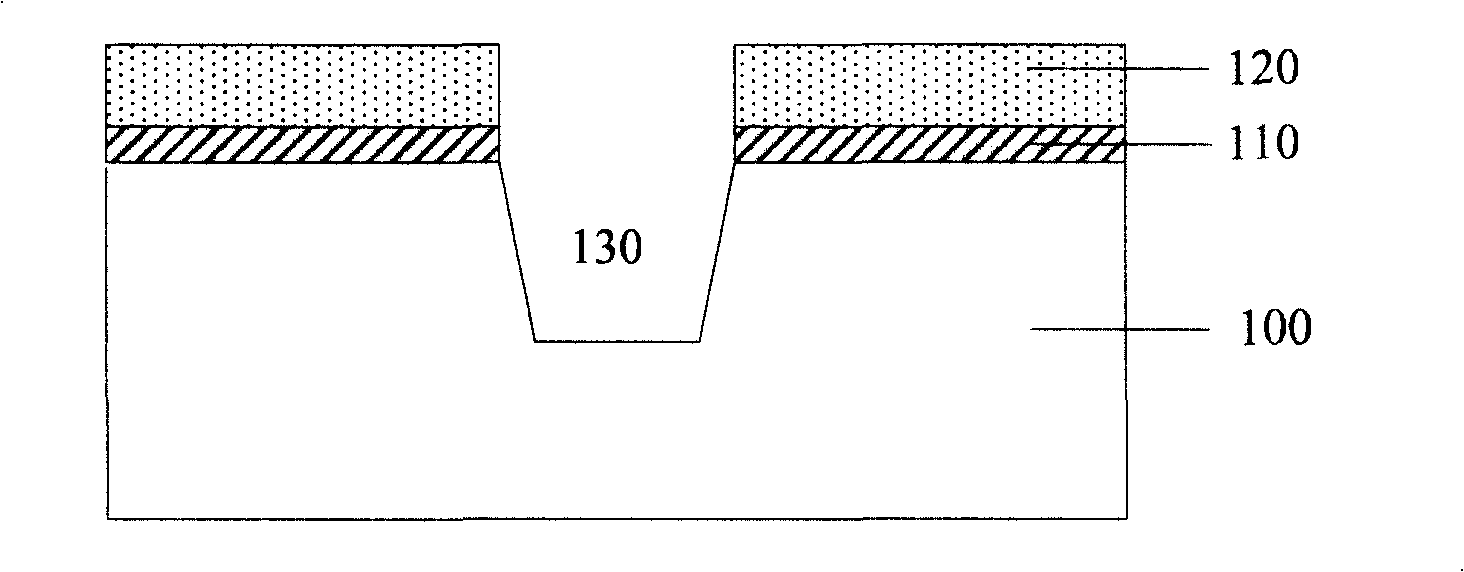

[0027] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0028] The manufacturing method of the semiconductor isolation structure of the present invention is to form a planarized isolation region between the active regions of the semiconductor device by using an oxygen ion implantation method on the semiconductor substrate with a sacrificial oxide layer formed on the surface, and the semiconductor substrate is Silicon on insulator, under the conditions of different ion implantation energies and ion doses, perform oxygen ion implantation one or more times, and then perform annealing treatment to form an isolation structure.

[0029] Reference attached Figure 7 Shown is a process flow chart of the method for forming the semiconductor isolation structure of the present invention. Such as Figure 7 As shown, the method for forming the isolation structure of the present invention includes: step S1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com