Read-write control circuit, method and apparatus for two-port RAM

A read-write control and dual-port technology, applied in the field of memory, can solve the problems of adding control logic, function logic cannot read parameters, and increasing the burden of DSP

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

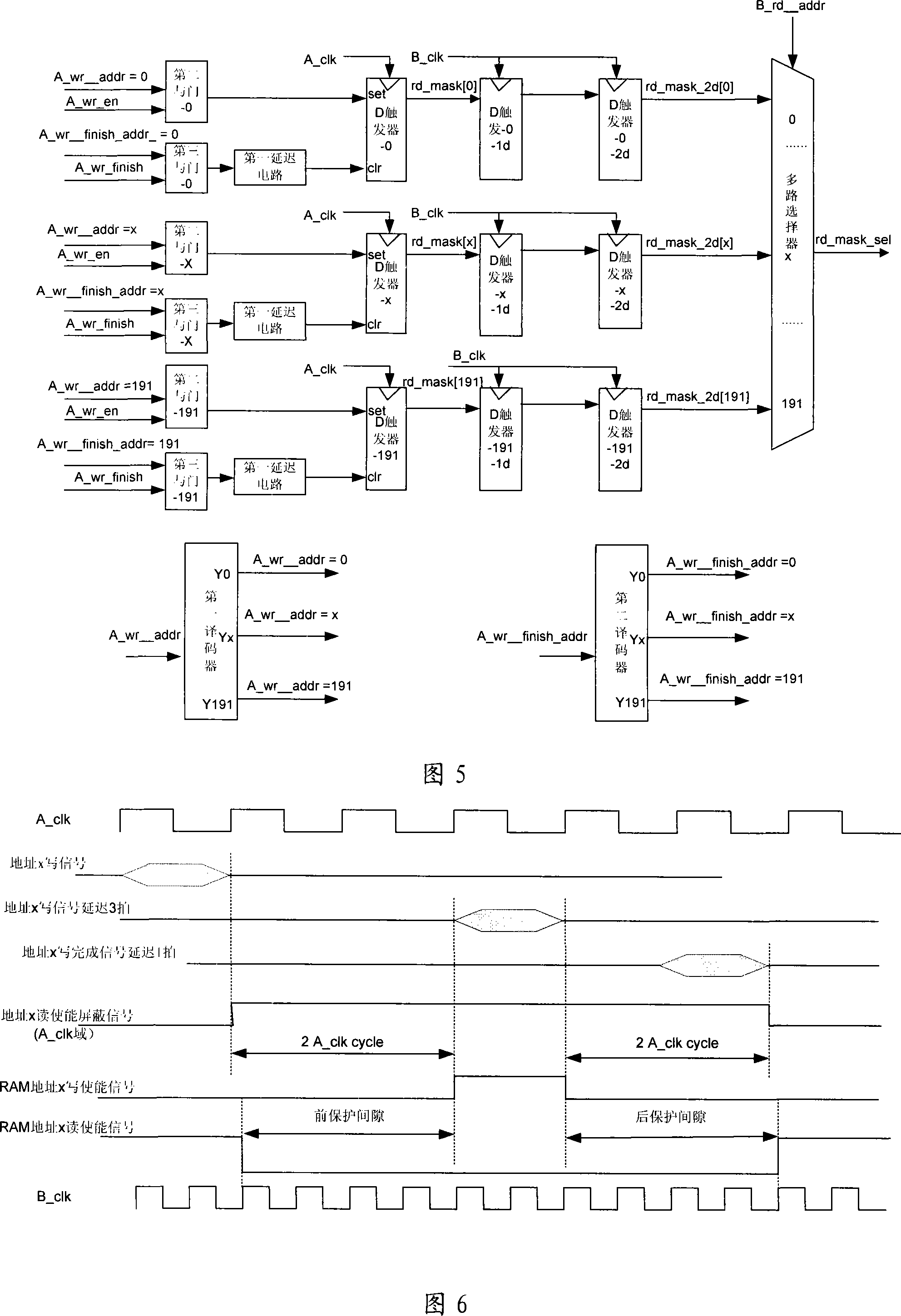

[0084] The first embodiment of the read-write control method of the dual-port RAM of the present invention, as shown in Figure 8, includes:

[0085] 801. Decode the first port address bus signal to generate a set of first port storage unit selection signals; the set of first port storage unit selection signals is at a high level at the output end corresponding to the first port address bus signal, low on the remaining outputs;

[0086] 802. Perform an AND operation on the group of first port storage unit selection signals and first port write enable signals respectively;

[0087] 803. Reverse respectively a group of first-port storage unit selection signals after AND operation;

[0088] 804. Before at least 3 clock cycles, output a group of first port memory unit selection signals after AND operation as a group of memory unit read mask signals; after at least 3 clock cycles, output a group of first port after inversion The memory cell selection signal is output as a group of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com