Wafer and semiconductor device testing method

A test method, semiconductor technology, applied in the field of wafers, can solve problems such as no description or hint, and achieve the effect of reducing the number

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] Hereinafter, the present invention will be described in detail using the illustrated embodiments.

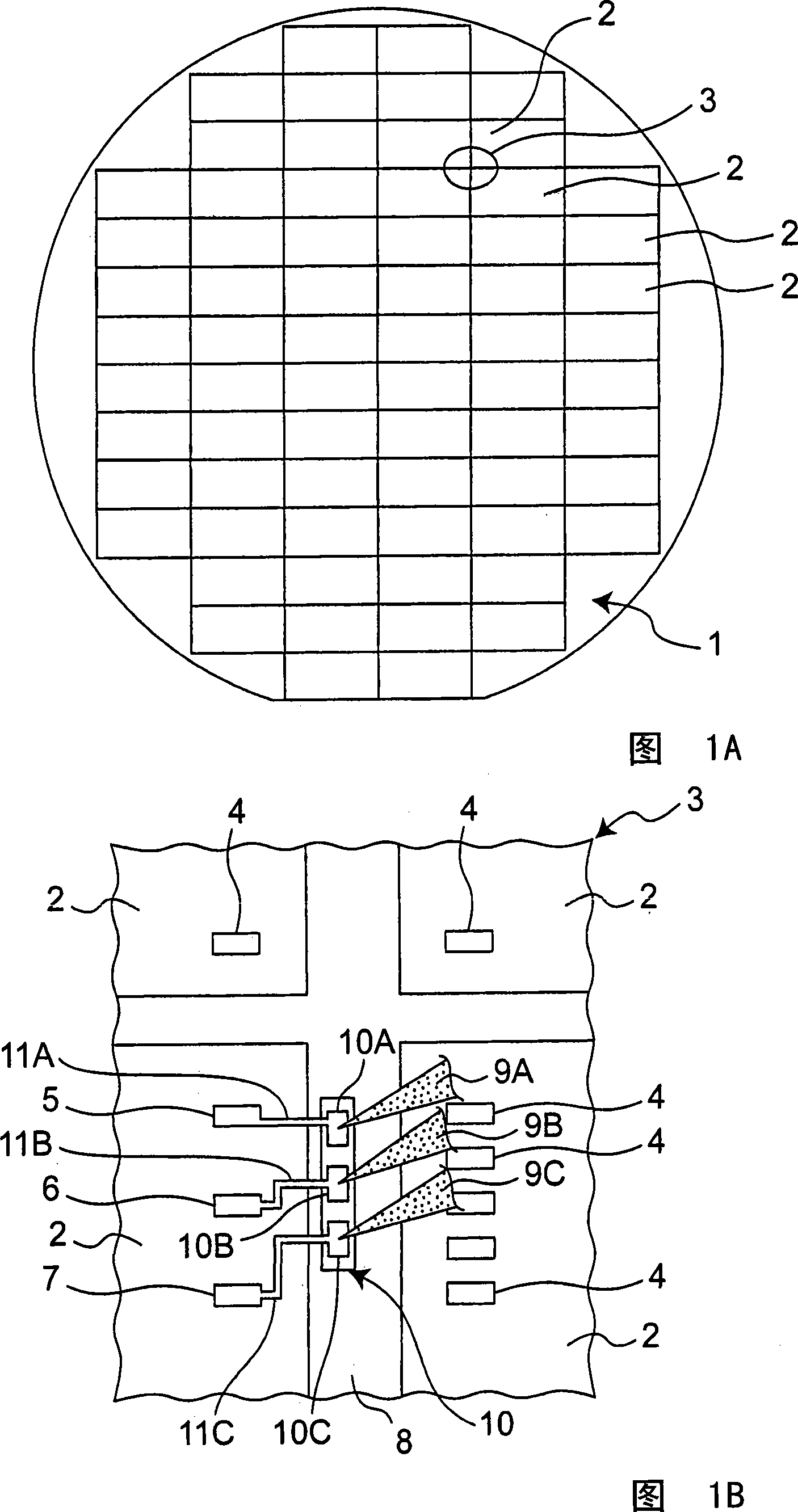

[0040]FIG. 1A shows a schematic structure of a wafer 1 according to one embodiment of the present invention. This wafer 1 is a wafer that has undergone a wafer process, and the surface of the wafer is divided into a plurality of rectangular areas (referred to as "chip areas") 2 like a general wafer. A semiconductor device (not shown) is produced in each chip region 2 .

[0041] FIG. 1B shows an enlarged portion of FIG. 1A , that is, a portion 3 where the corners of the four chip regions 2 are concentrated. As shown in FIG. 1B , chip regions 2 are separated from each other by dicing lines (also referred to as dividing lines) 8 having a fixed width. Then, after the wafer test described later is completed, the wafer 1 is divided into chips along the dicing lines 8 . A plurality of pads 4 for inputting and outputting signals between elements in the chip area and the outsid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com