Concurrent hardware selftest for central storage

A computer system and storage system technology, applied in the field of computer system design, can solve the problems of data clearing or disturbance, achieve the effect of flexible and efficient design, and improve system performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

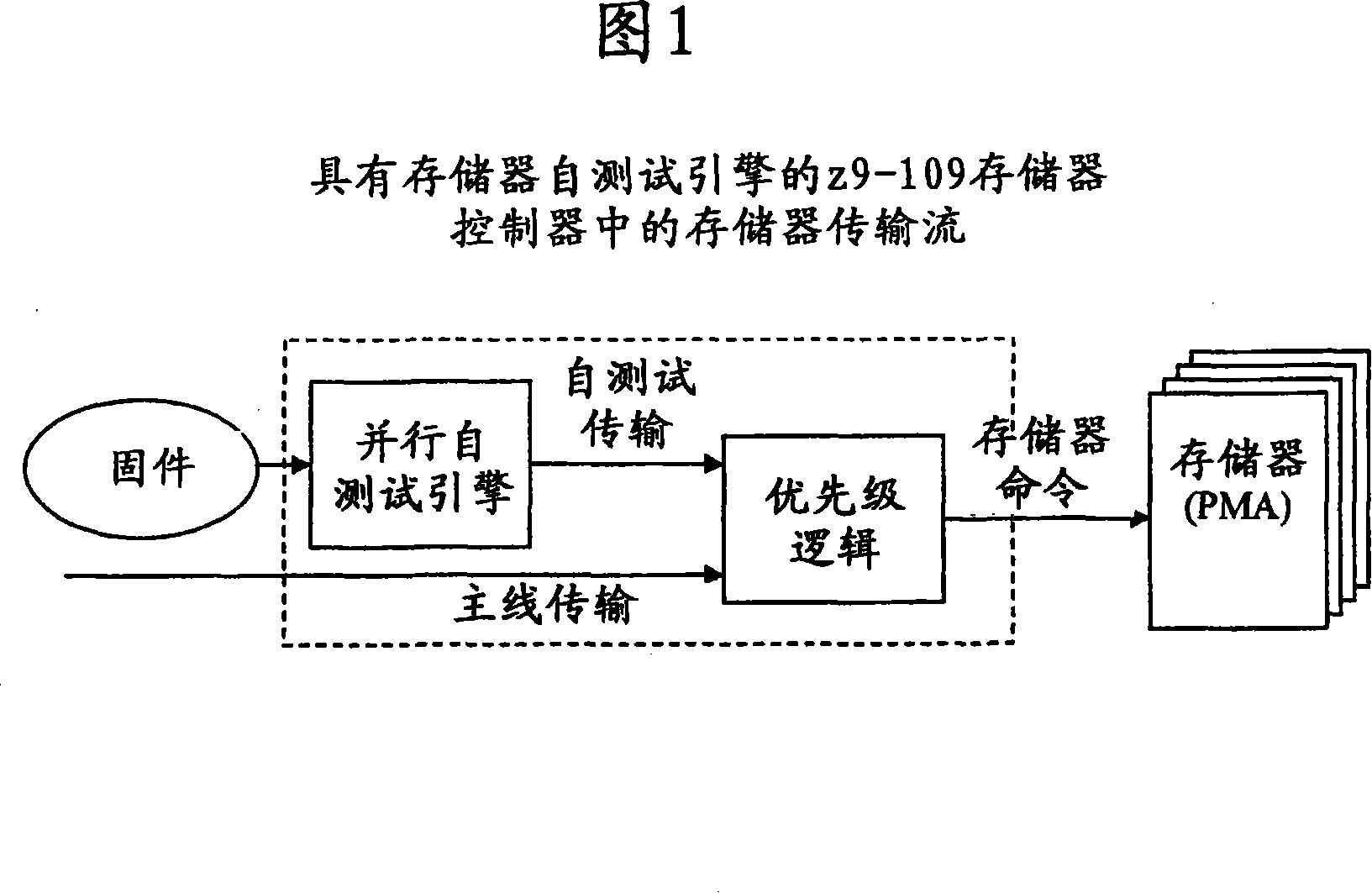

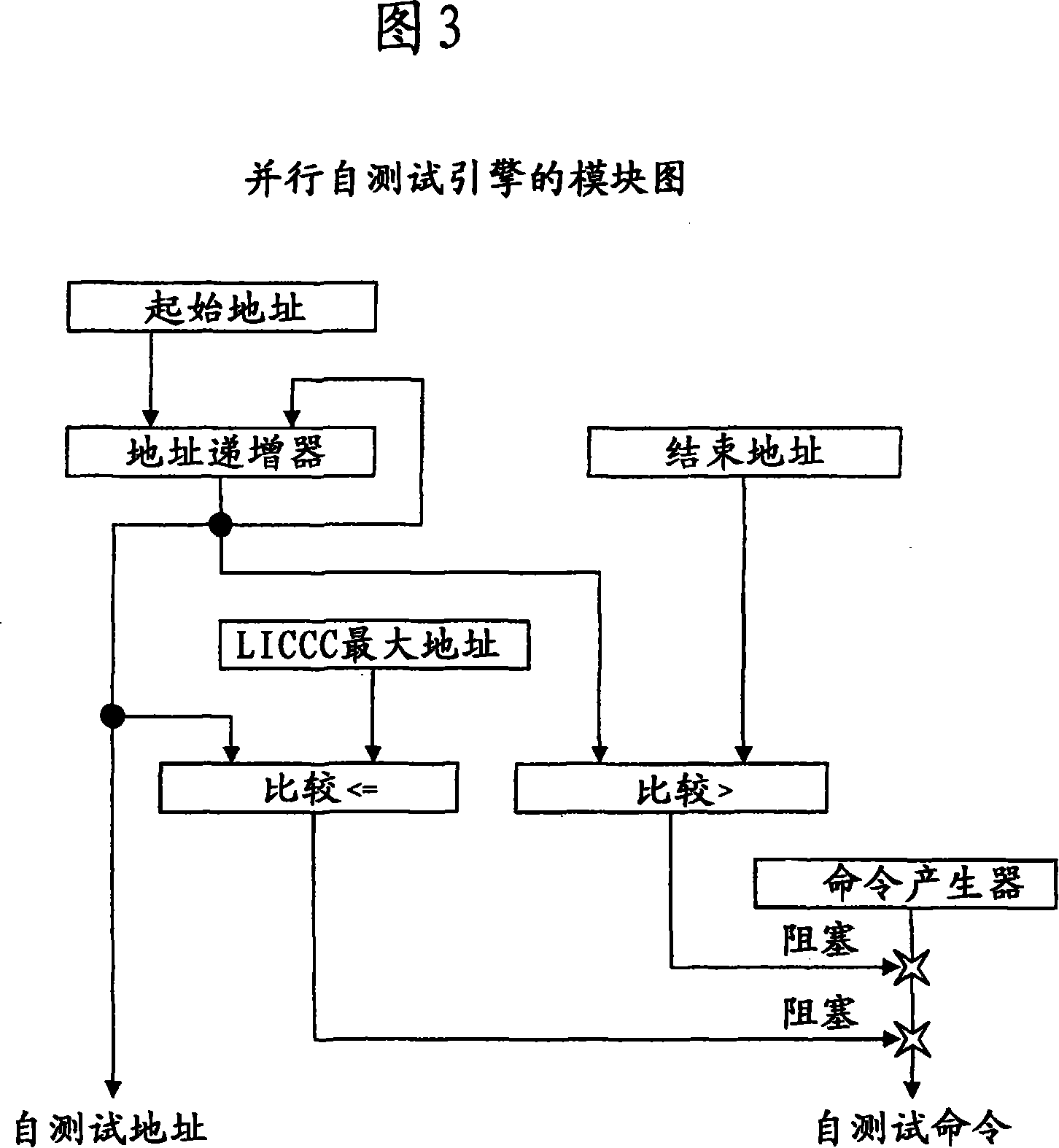

[0019] The present invention is implemented using parallel self-test hardware provided with a system that contains two main pieces of hardware: a self-test engine and priority logic. When parallel self-test is required, the hardware self-test engine is first set up by firmware. The start and end addresses, address mode, and data mode are initialized. After being set up according to the firmware, the self-test engine will start sending fetch and store commands to the priority logic in the background. Priority logic will take commands from the self-test engine and normal mainline transfers, prioritize them, and send them sequentially to the Processor Memory Array (PMA) portion of the memory subsystem.

[0020] Referring now to the drawings in more detail, it can be seen that Figure 1 is a system block diagram showing how memory transfers are handled.

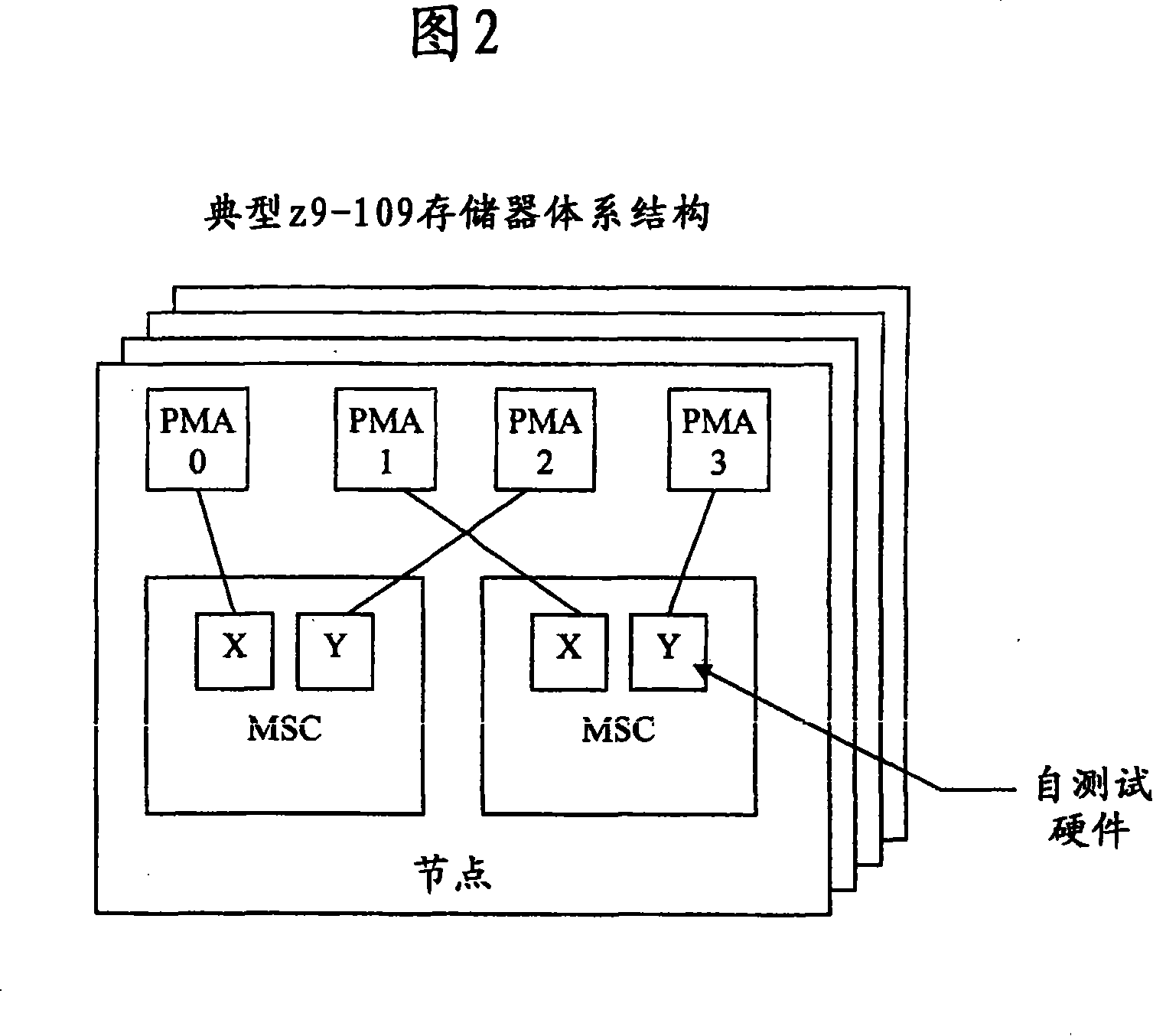

[0021] In the z9-109 implementation, the MSC (Main Storage Controller) chip has an X port and a Y port, each independently con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com