Method of fabricating a tunneling nanotube field effect transistor

A field effect transistor, nanotube technology, used in transistors, nanotechnology, nanotechnology, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention is a method of fabricating tunneling nanotube field effect transistors using selectively doped portions of nanotubes. Herein, the term "nanotube" is used interchangeably for nanotubes and nanowires (ie, nanotubes without axial openings). The method can be used to fabricate ultra-large scale integration (ULSI) circuits and devices.

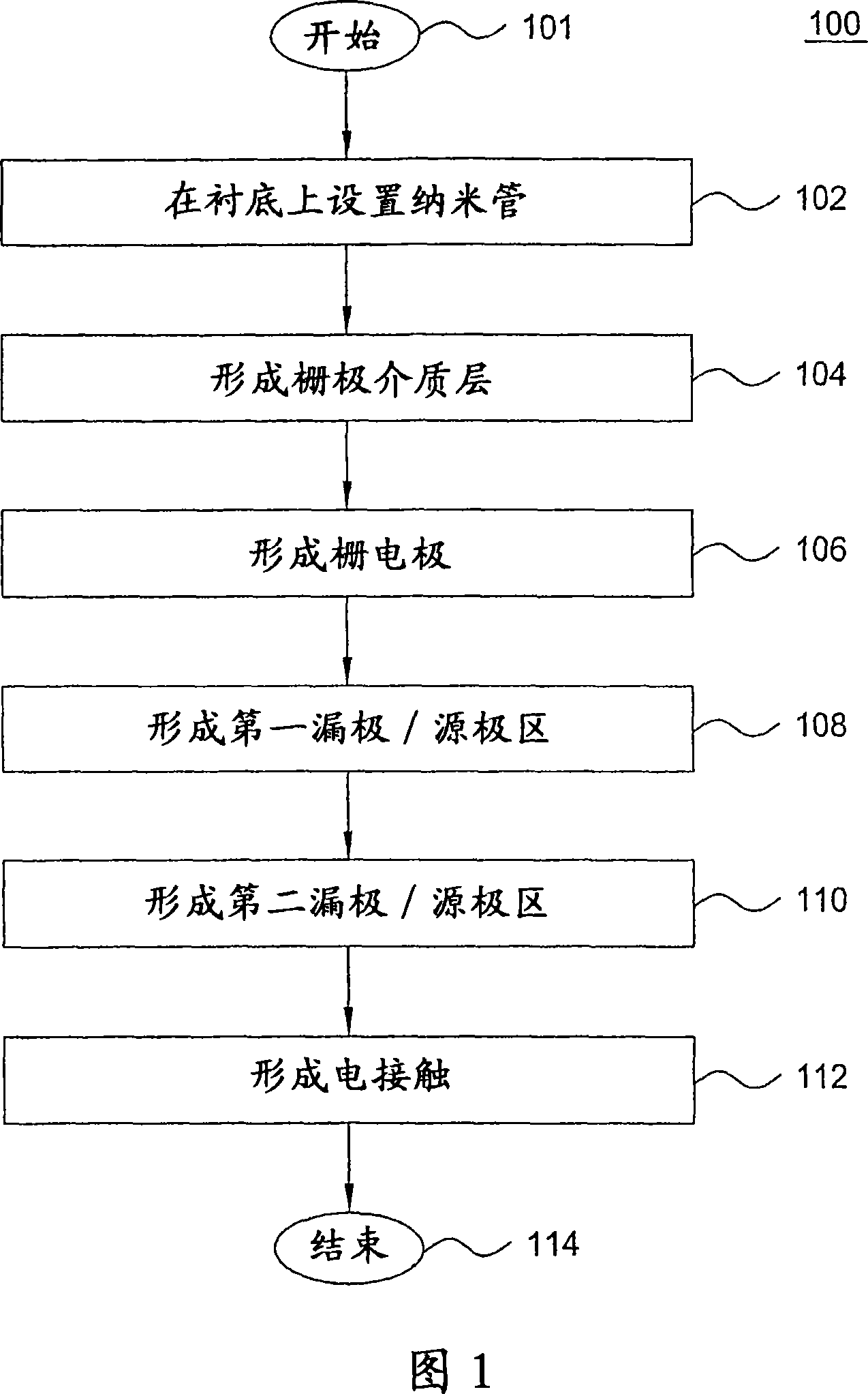

[0017] FIG. 1 shows a flowchart of one embodiment of a method of the present invention for fabricating a tunneling nanotube field effect transistor as method 100 . The method 100 includes processing steps performed on a substrate in which at least one tunneling nanotube field effect transistor is fabricated. In an exemplary embodiment, the processing steps are performed sequentially, in the order shown. In alternative embodiments, at least two processing steps may be performed simultaneously or in a different order. Conventional sub-processes such as application and removal of photolithographic masks or sacrificial a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com