A high speed dram architecture with uniform access latency

A dynamic random access and memory technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of DRAM array bit density reduction, noise coupling mismatch, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

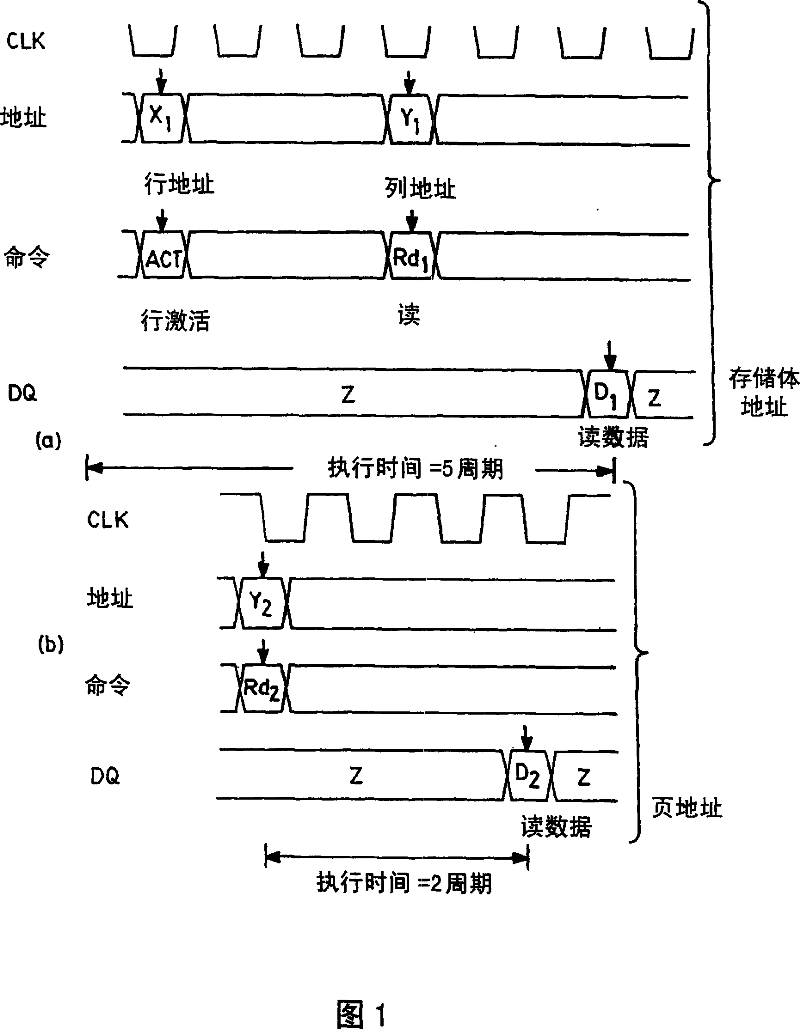

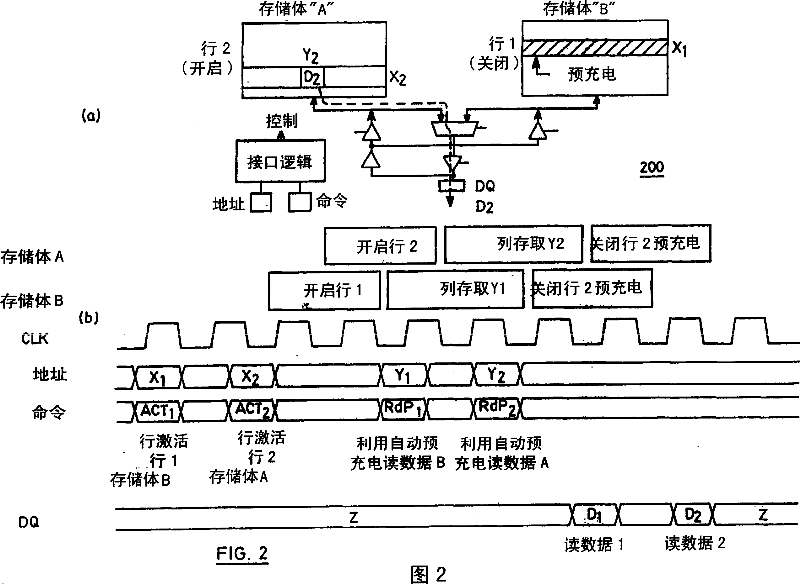

[0034] In order to obtain high-speed performance, the DRAM structure is optimized regardless of the addressing mode of its continuous memory access operations, and each read, write or refresh operation has the same timing. This is different from traditional DRAM architectures where operation timing depends on the value of the target address and the history of the last memory operation.

[0035] Obtaining the same access timing for all memory commands is achieved by performing a complete row access operation for each read, write or refresh command received. A complete row access operation includes word line maintenance, memory cell readout, bit line readout, cell information recovery, word line separation maintenance, and bit line compensation and pre-charging. The following description will address implementation details that allow memory devices and memory macros fabricated using conventional DRAM processing techniques to perform data accesses with execution times and cycle t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com