Method for generating testing vector

A technology of test vectors and synchronous clocks, which is applied in electronic circuit testing, automatic power control, electrical components, etc., and can solve problems such as rising chip manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and embodiments.

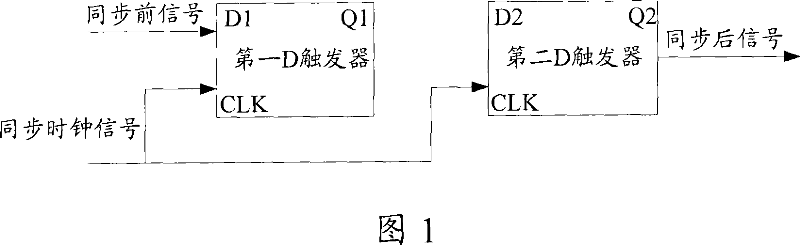

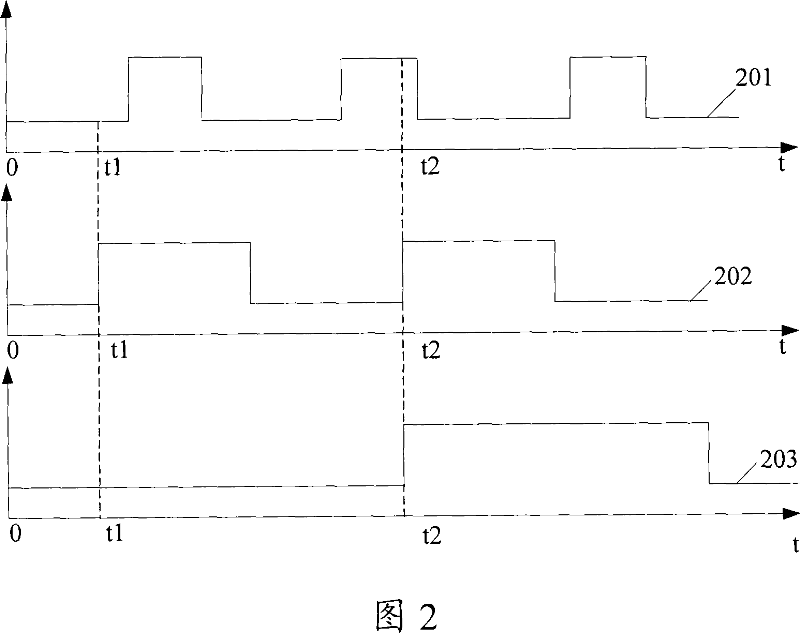

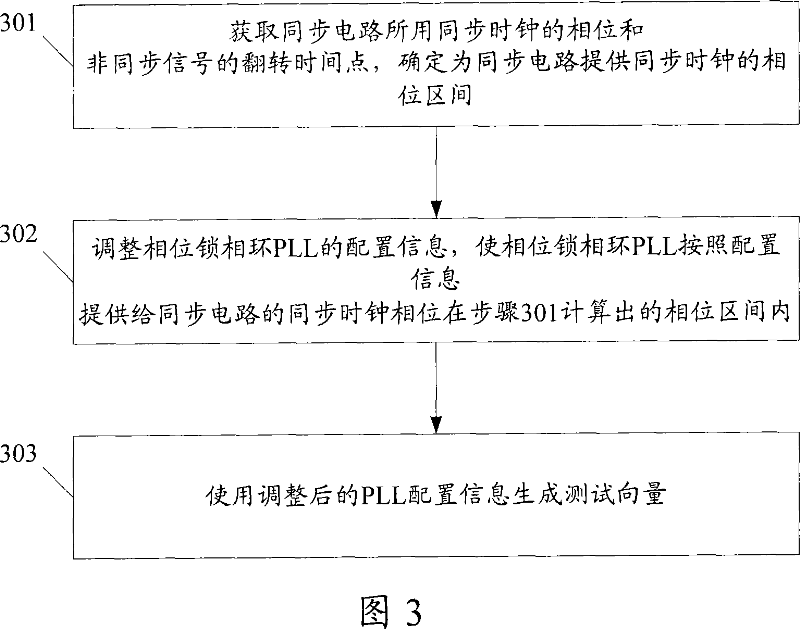

[0032] The method for generating test vectors provided by the present invention first obtains the phase of the synchronous circuit synchronous clock and the flipping time point of the asynchronous signal, and determines the phase interval of the synchronous clock for the synchronous circuit; secondly, adjusts the configuration information of the phase-locked loop PLL, so that The synchronous clock phase output by the PLL according to the configuration information is within the calculated phase interval; finally, the adjusted PLL configuration information is used to generate a test vector.

[0033] The method for generating test vectors provided by the present invention will be described in detail below.

[0034] Referring to Fig. 3, Fig. 3 is a flow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com