Double channel DSPEED-ADC_D2G high-speed data collecting plate

A high-speed data acquisition and data acquisition technology, applied in signal transmission systems, instruments, electrical signal transmission systems, etc., can solve the problems of single working mode, only one trigger mode, slow external transmission interface rate, etc., and achieve strong signal processing. effect of ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] The present invention will be further described below in conjunction with accompanying drawing and specific embodiment:

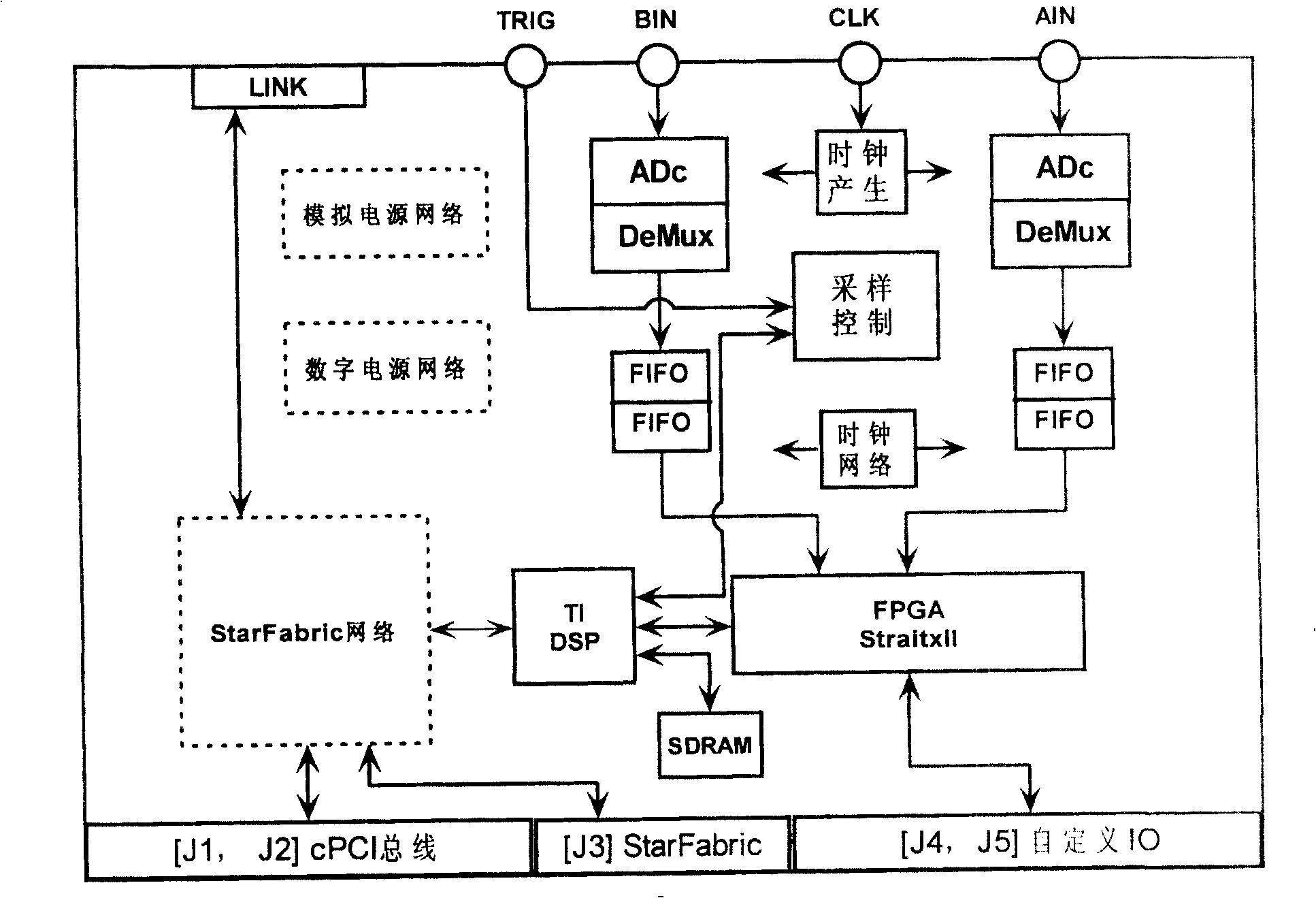

[0013] This ultra-high-speed data acquisition board includes two relatively independent data acquisition channels, each channel includes: an ADC chip model TS83102G0, a data shunt (DeMux) chip model TS81102G0, and 4 FIFO chips model IDT72T40118 . See attached figure 1 , attached figure 2 .

[0014] The sampling clock of ADC is 2 GHz sinusoidal signal provided externally through SMA, and the comparator in the board generates a square wave clock, which is provided to two ADCs. The input signals of the two ADCs are input by two SMAs and directly sent to their respective ADC chips. The ADC outputs the 10-bit data and clock after analog-to-digital conversion to the DeMux chip. The DeMux chip splits the input high-speed data stream into 8-way 10-bit low-speed data stream and slow clock input FIFO module.

[0015] Each channel FIFO is composed of two...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com