Computer implemented system and method for generating a layout of a cell defining a circuit component

a technology of circuit components and computer implementation, applied in the field of computer implemented systems and methods for generating circuit component layouts, can solve the problems of increasing the complexity of the design rules, the complexity of the design of standard cells for emerging process technologies, and the complexity of the techniques used to develop each of the process layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

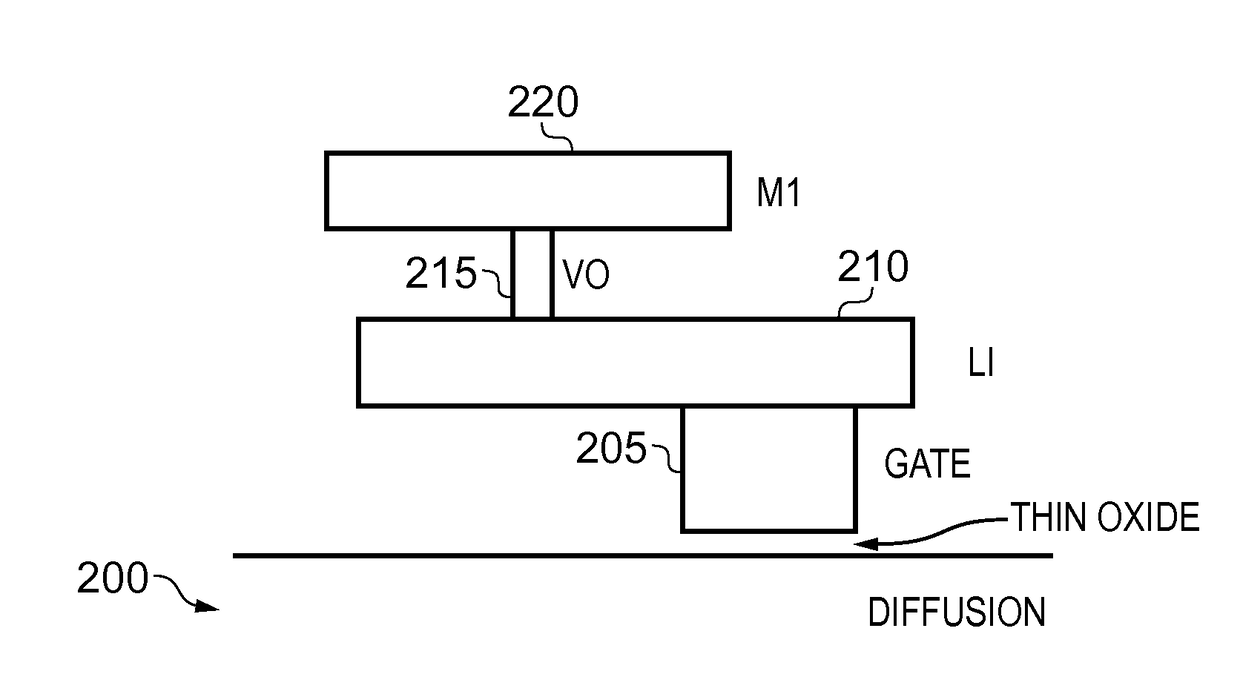

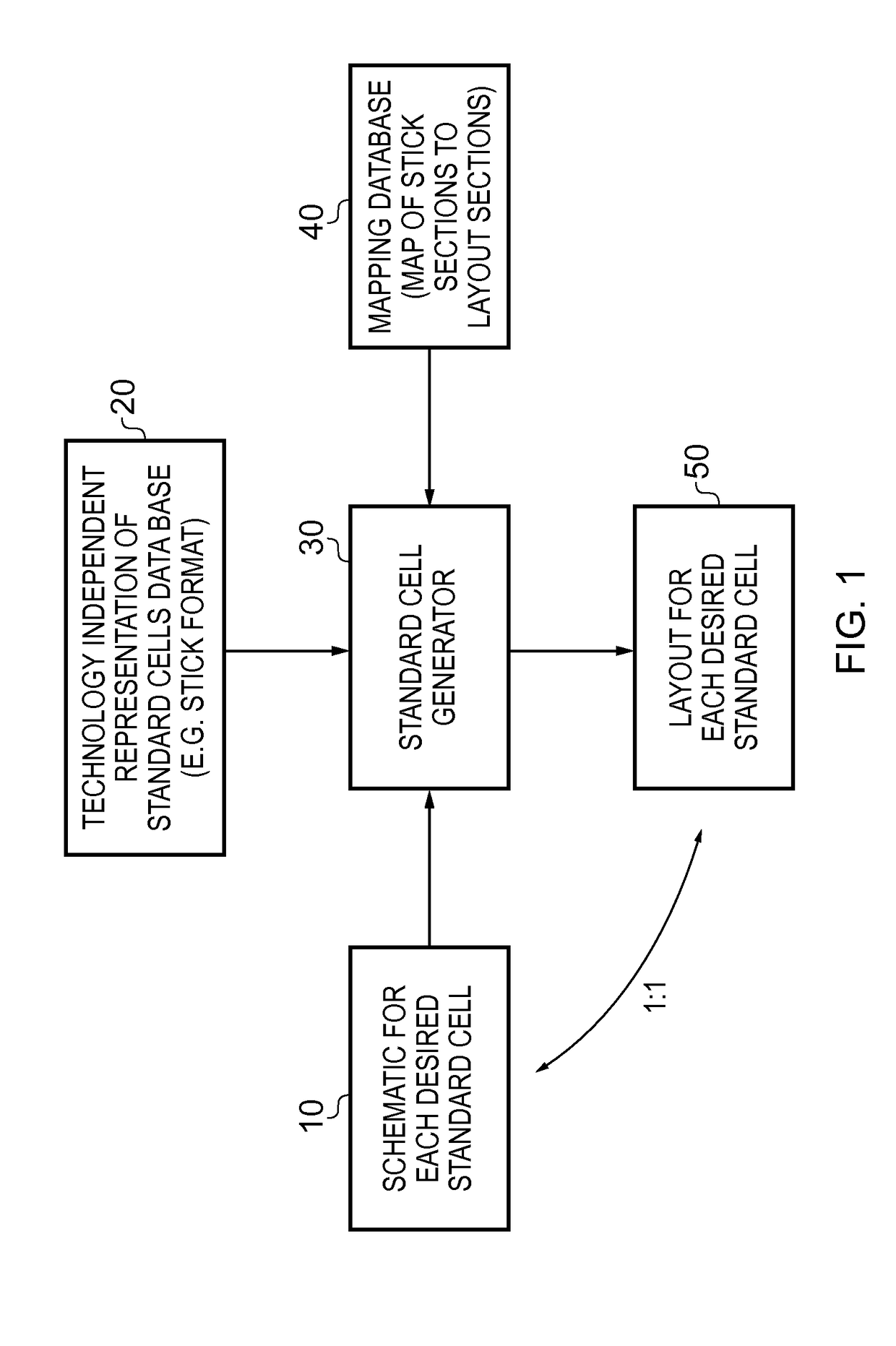

[0061]Before discussing the embodiments with reference to the accompanying figures, the following description of embodiments is provided. In one example, there is provided a computer implemented method of generating a layout of a cell defining a circuit component, the layout providing a layout pattern for a target process technology, the method comprising: obtaining an archetype layout providing a valid layout pattern for the cell having regard to design rules of the target process technology; receiving an input data file providing a process technology independent schematic of the circuit component for which the cell is to be generated; performing a schematic sizing operation on the input data file, having regard to schematic constraints applicable to the target process technology and layout constraints derived from the archetype layout, in order to generate an output data file providing a process technology dependent schematic of the circuit component; performing a cell generation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com