Analog-to-digital conversion circuit

a conversion circuit and analog-to-digital technology, applied in analogue/digital conversion, transmission systems, instruments, etc., can solve the problems of increasing the range of applications of parallel-type analog-to-digital conversion systems, increasing power consumption and chip size correspondingly, and reducing the range of offset variations. , the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

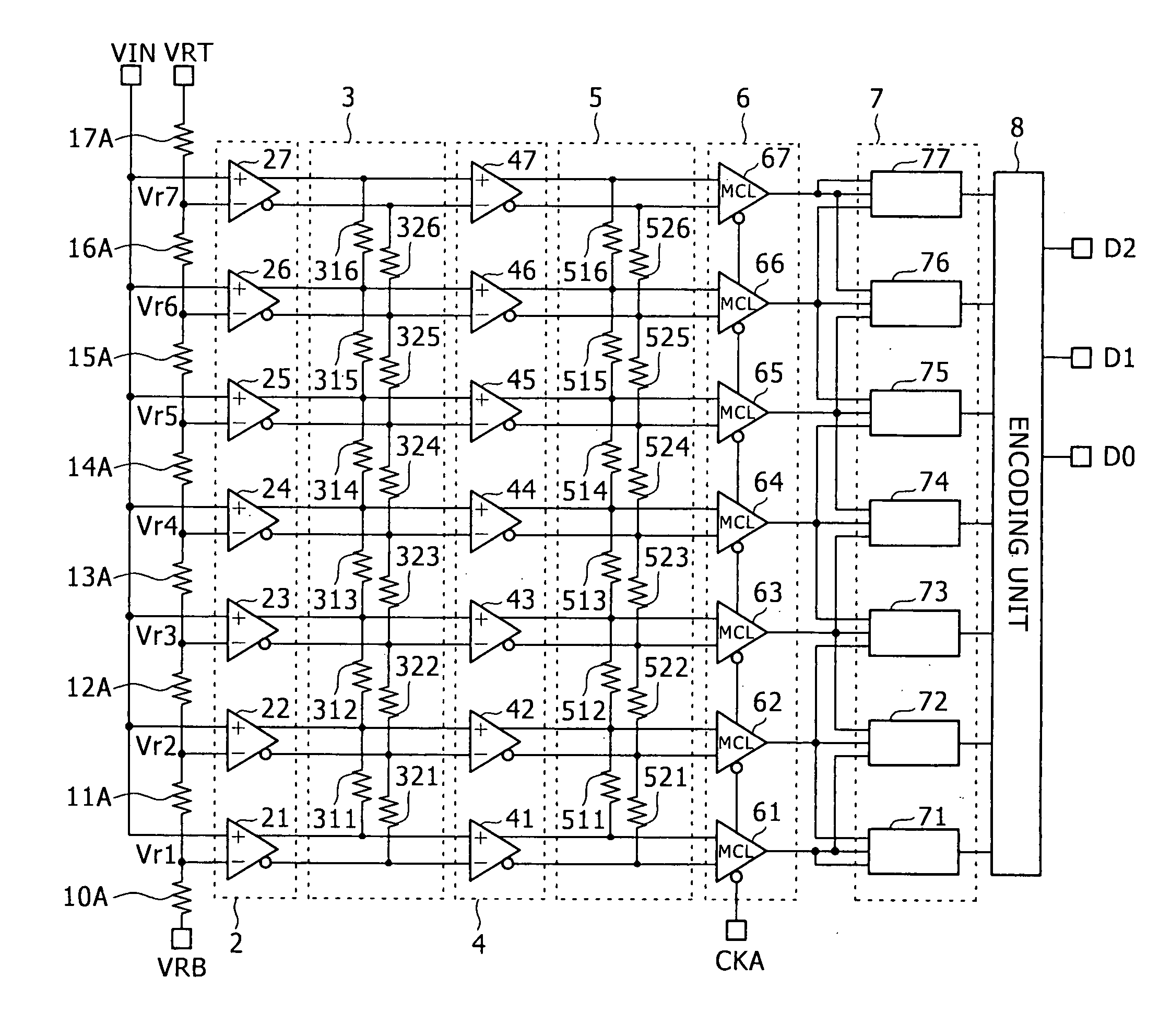

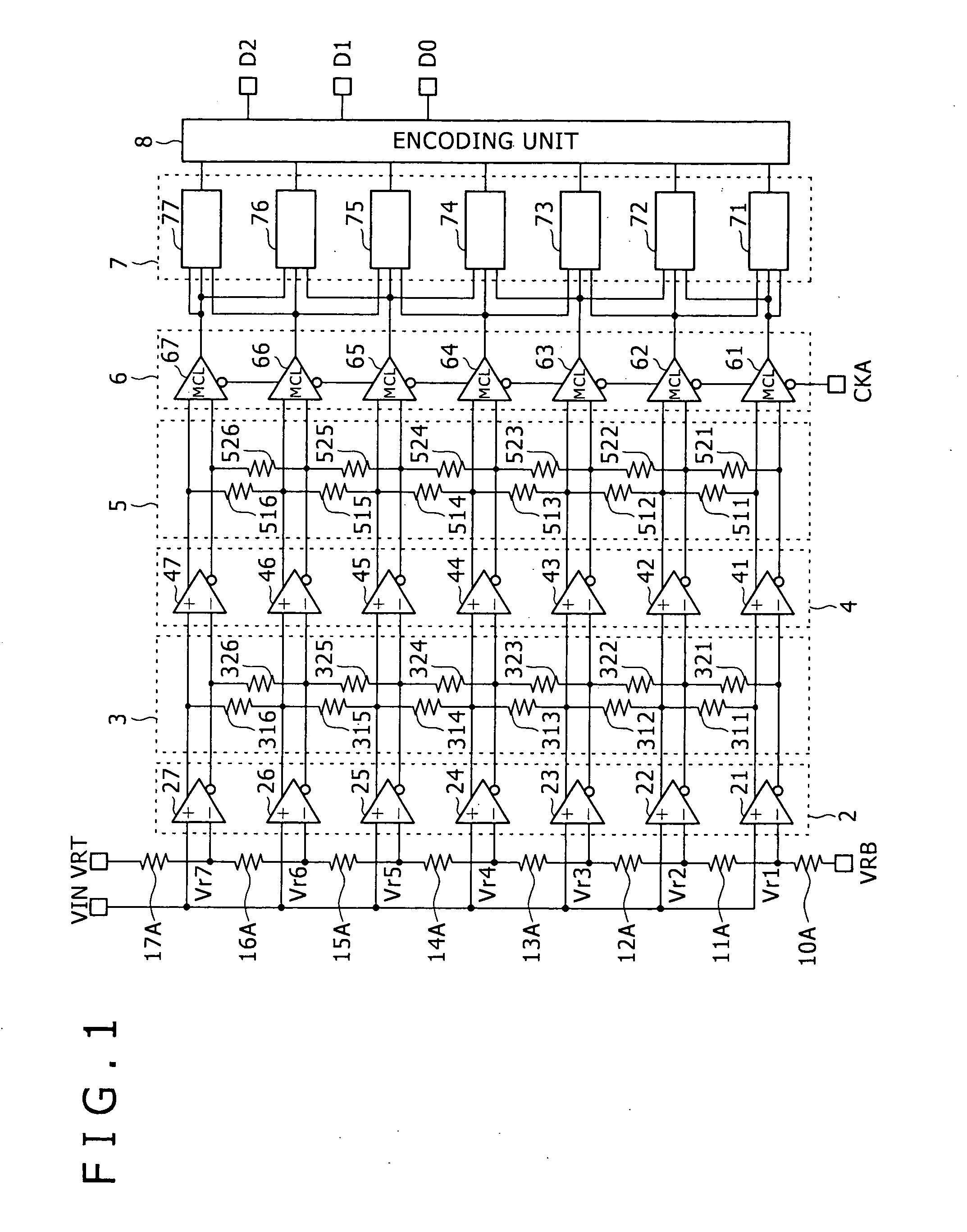

[0029]FIG. 1 is a diagram showing an example of configuration of a three-bit analog-to-digital conversion circuit according to a first embodiment of the present invention.

[0030] The analog-to-digital conversion circuit shown in FIG. 1 includes resistive elements 10A to 17A for generating reference voltages, a first amplifying unit 2, a first averaging unit 3, a second amplifying unit 4, a second averaging unit 5, a comparing unit 6, a third averaging unit 7, and an encoding unit 8.

[0031] The first amplifying unit 2 is an embodiment of a first amplifying unit according to the present invention.

[0032] The second amplifying unit 4 is an embodiment of a second amplifying unit according to the present invention.

[0033] The first averaging unit 3 is an embodiment of a first averaging unit according to the present invention.

[0034] The second averaging unit 5 is an embodiment of a second averaging unit according to the present invention.

[0035] The comparing unit 6 is an embodiment of a...

second embodiment

[0097] A second embodiment of the present invention will next be described.

[0098] An analog-to-digital conversion circuit according to the second embodiment is provided with a folder circuit and an interpolating circuit.

[0099]FIG. 6 is a diagram showing an example of configuration of the three-bit analog-to-digital conversion circuit according to the second embodiment of the present invention.

[0100] The analog-to-digital conversion circuit shown in FIG. 6 has resistive elements 10A to 15A for generating reference voltages, a first amplifying unit 2A, a first averaging unit 3A, a folder circuit 9, a coarse amplifier 10, an interpolating circuit 11, a second averaging unit 5A, a comparing unit 6A, a third averaging unit 7A, and an encoding unit 8.

[0101] The first amplifying unit 2A is an embodiment of a first amplifying unit according to the present invention.

[0102] The folder circuit 9 is an embodiment of a folder circuit according to the present invention.

[0103] The coarse amp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com