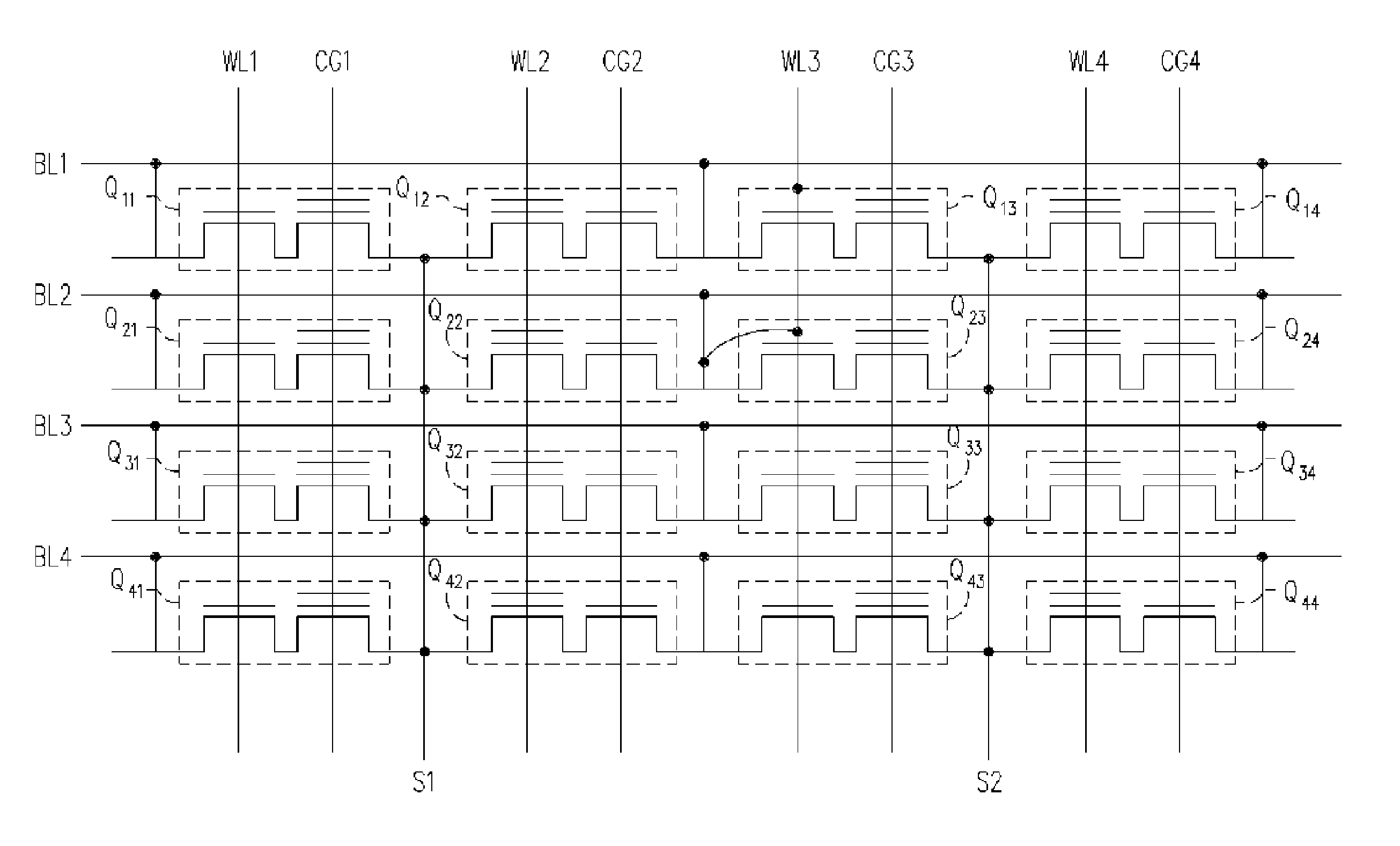

Failure test method for split gate flash memory

a failure test and flash memory technology, applied in static storage, digital storage, instruments, etc., can solve the problems of reducing affecting the stability of the memory, and affecting the stability of the whole chip, so as to avoid the complicated analysis process and reduce the time for analyzing the memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

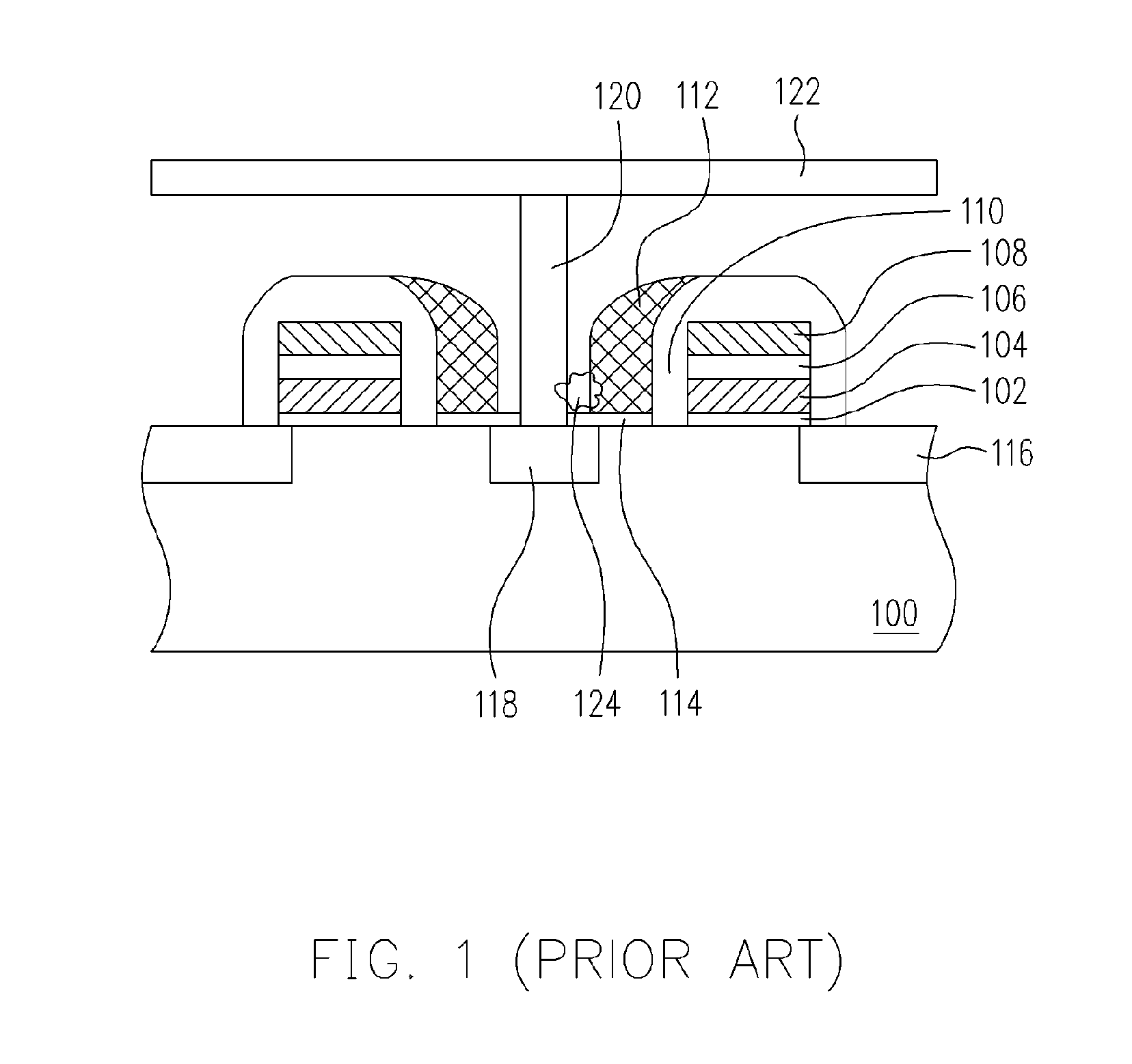

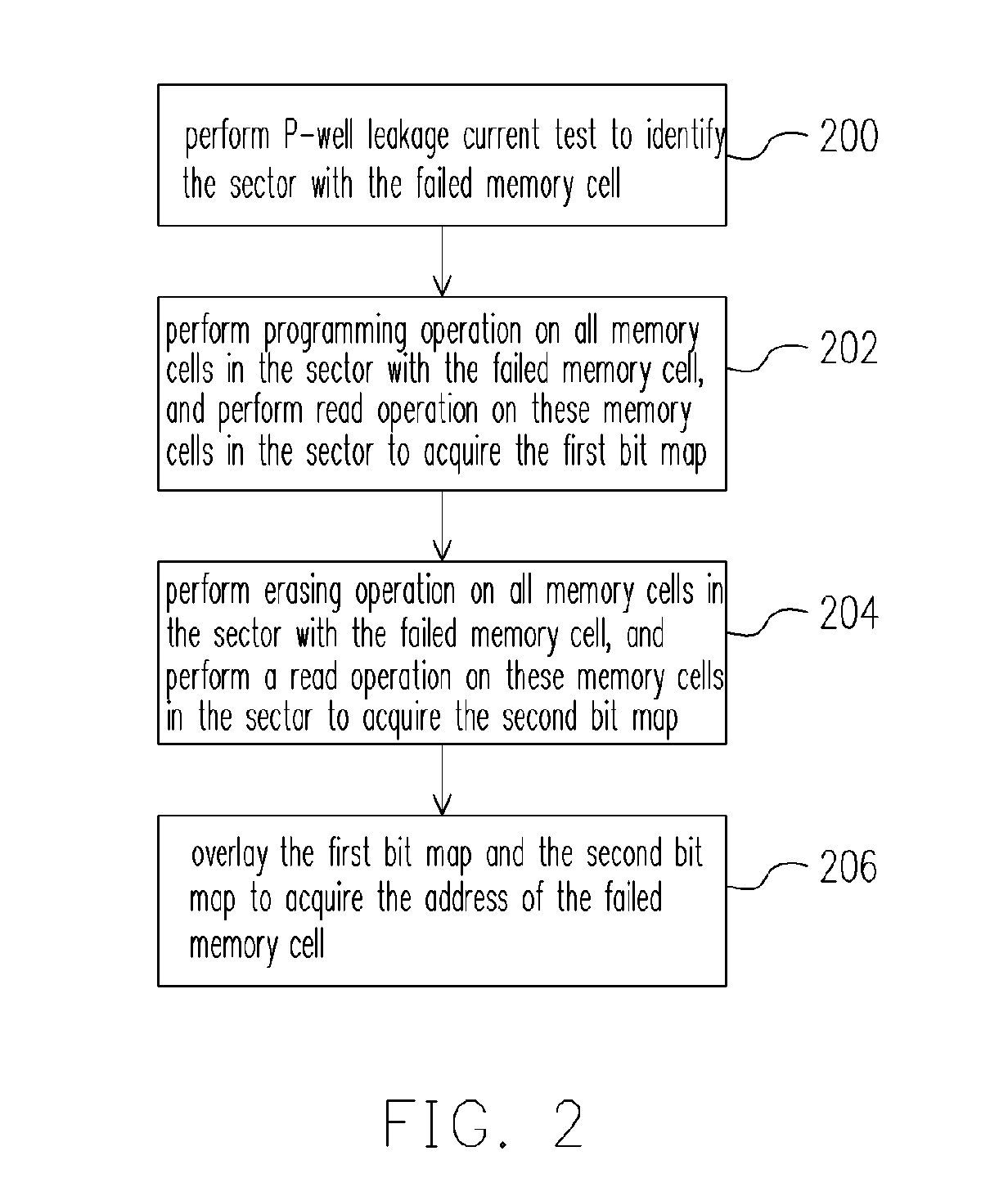

[0027]FIG. 2 is a flowchart showing a failure test method for a split gate flash memory according to an embodiment of the present invention. FIG. 3 is a schematic drawing showing an operation of a P-well leakage-current test for memory cells according to an embodiment of the present invention. In the following description, the failed memory cell is the memory cell where the word line-bit line short circuit occurs.

[0028] Referring to FIG. 2, the P-well leakage-current test is performed to identify the sector with the failed (defective) memory cell in the step 200. The P-well leakage-current test comprises, for example, applying 2V to the word line of the memory cell, and applying 8V to the substrate, i.e. the P-well, to measure current value of sectors as shown in FIG. 3. If a sector is a normal sector, the current measured is lower than 20 μA. When a sector contains a failed memory cell, a P-well leakage current is generated and the current measured is higher than 20 μA. For exampl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com