High speed low power 4-2 compressor

a compressor and low power technology, applied in the field of logic circuits, can solve the problems of increasing the complexity of the multiplier circuit, increasing the cost of the circuit, and increasing the number of circuits required

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

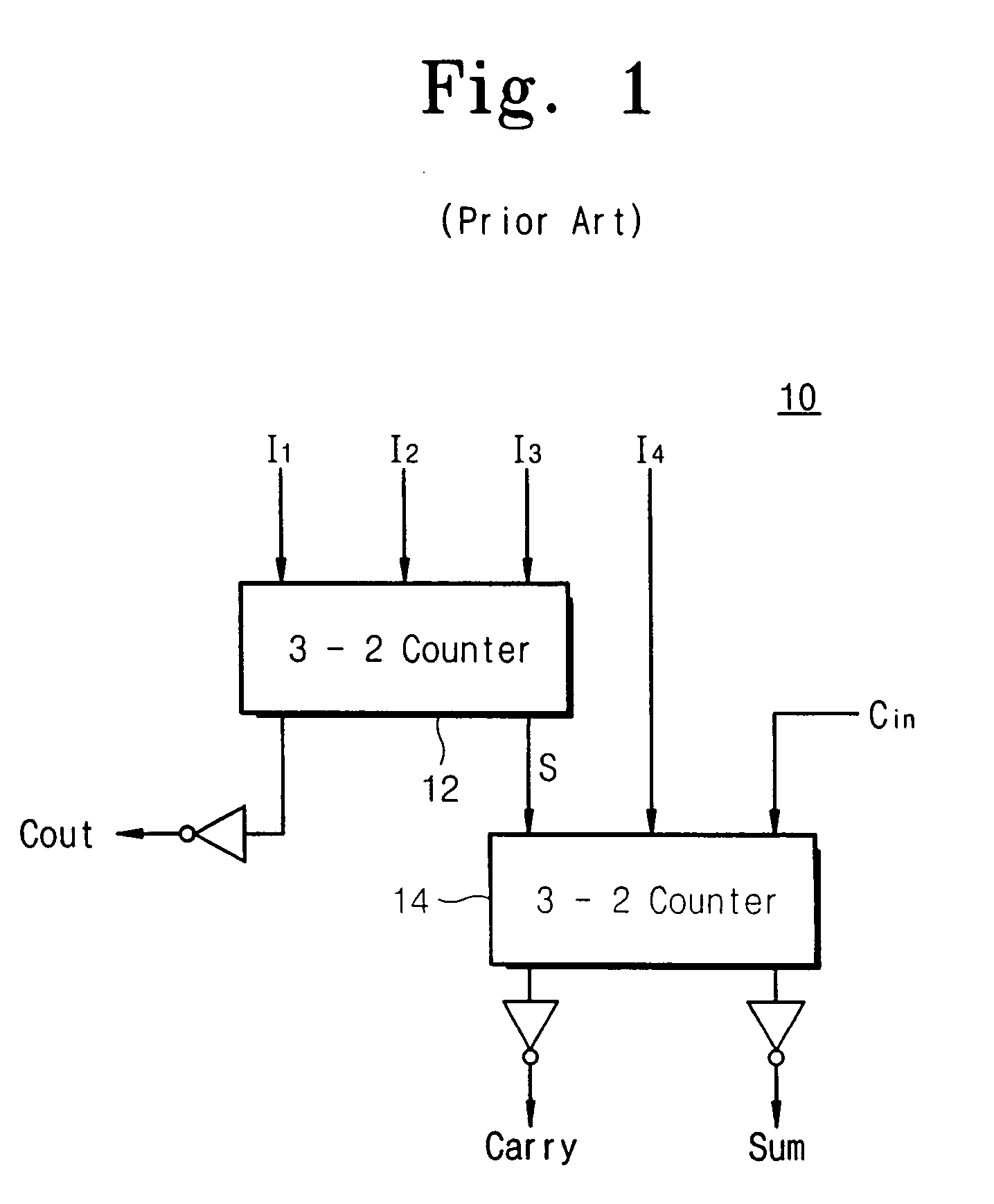

Image

Examples

Embodiment Construction

[0036]FIG. 6 is a circuit diagram for illustrating a 4-2 compressor 100 according to a preferred embodiment of the present invention. FIG. 7A is a detailed circuit diagram for illustrating an XOR / XNOR logic circuit shown in FIG. 6. FIG. 7B is a detailed circuit diagram for illustrating another embodiment of XOR / XNOR logic element using the NAND / NOR logic element shown in FIG. 6, and FIG. 8 is a detailed circuit diagram for illustrating a single railed multiplexer shown in FIG. 6.

[0037] Referring first to FIG. 6, the 4-2 compressor 100 comprises four logic circuits 110, 120, 130 and 140. The first logic circuit 110 generates a NAND / NOR result of externally input first and second data I1 and I2, and an XOR / XNOR result by using the NAND / NOR result, and generates a carry-out bit Cout in response to the NAND / NOR result. The second logic circuit 120 generates a selection signal, in response to the NAND / NOR results from the first logic circuit 110 and externally input third and fourth inp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com