Method and device for managing transmitting buffer area in field programmable gate array

A technology for sending buffers and buffers, applied in memory address/allocation/relocation, electrical components, transmission systems, etc., to solve problems such as occupying memory blocks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in further detail below in conjunction with the accompanying drawings.

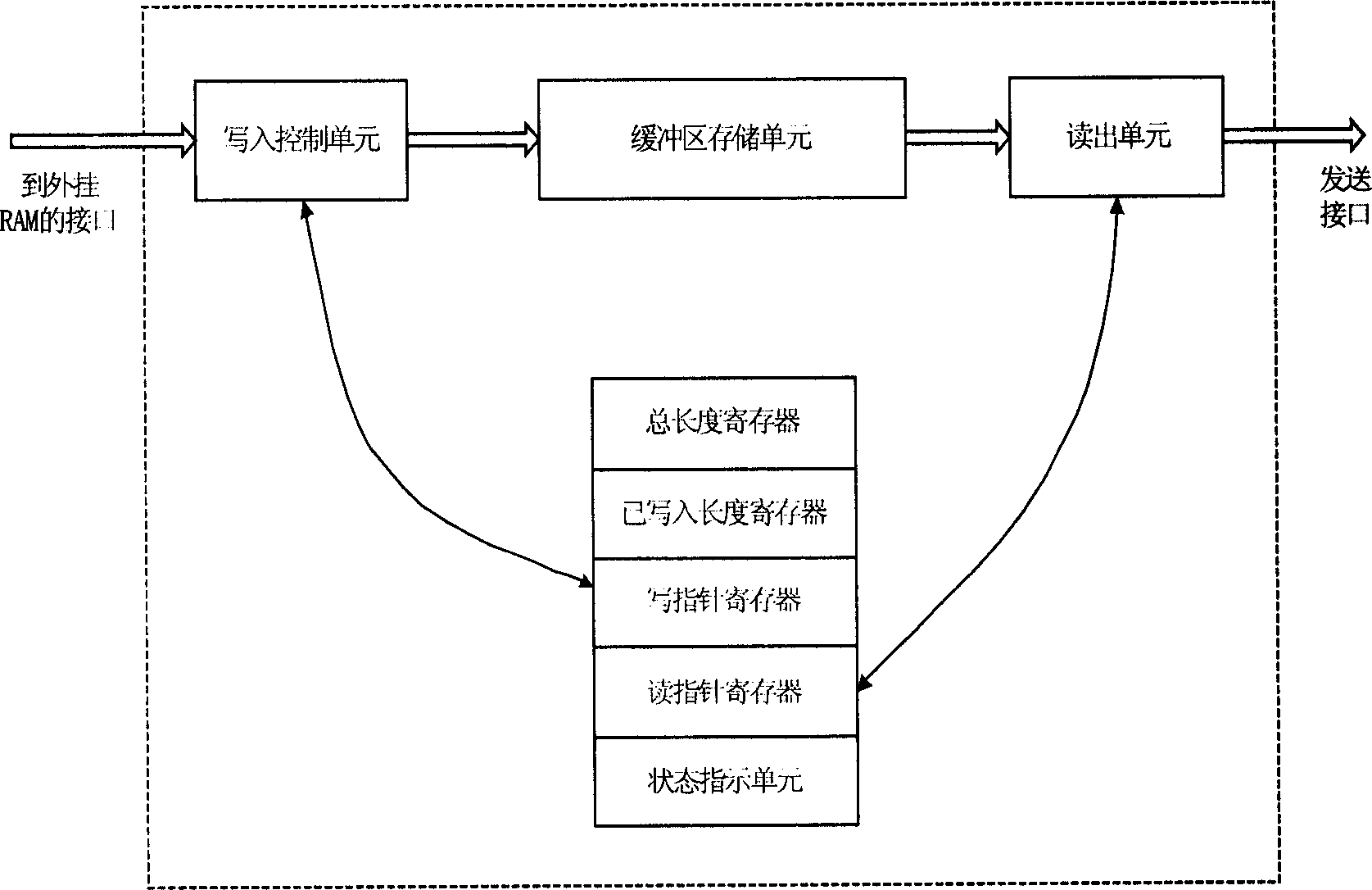

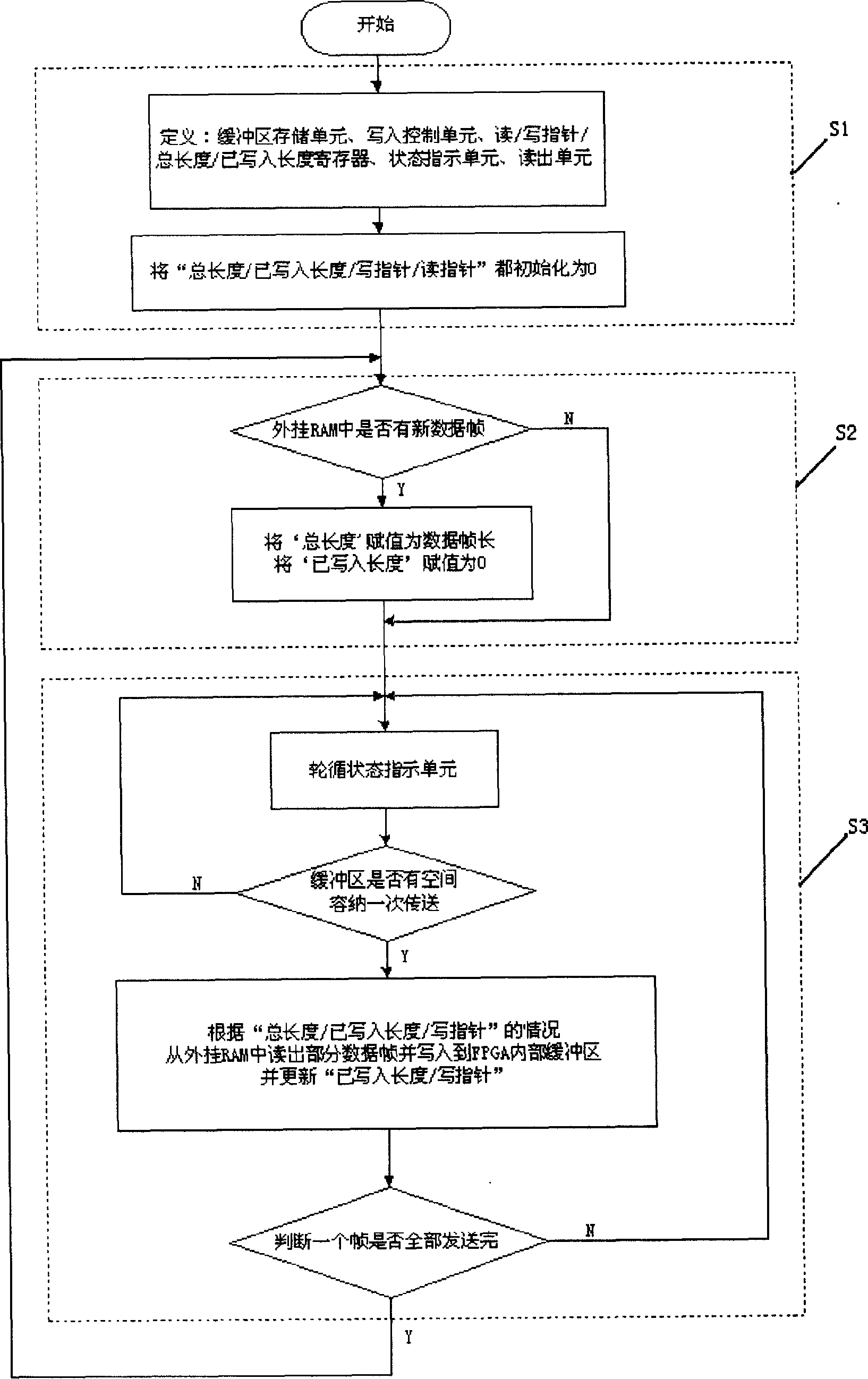

[0029] exist figure 1 Shown is the structural diagram of the present invention in the case of a single channel. When there is a data packet in the external RAM, the write control unit continuously inquires the status indicator unit, and if it is found to be '1', it means that the data that can be transmitted once can be accommodated, and then it is ready to write. The write control unit first refers to the "total length / written length register" to determine the length of a part of the data frame that needs to be transmitted at one time. The specific method is: subtract the written length register from the total length of the data frame to obtain the length of the remaining part of the frame. Before the data frame is written into the buffer, the written length register should be 0, and the length of the remaining part of the frame at this time is equal to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com