Integrated circuit with automatic pin-strapping configuration

A technology for integrated circuits and configuration circuits, which is applied in the direction of logic circuits using specific components, logic circuits, logic circuits using basic logic circuit components, etc., and can solve problems such as impractical fine-tuning of chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

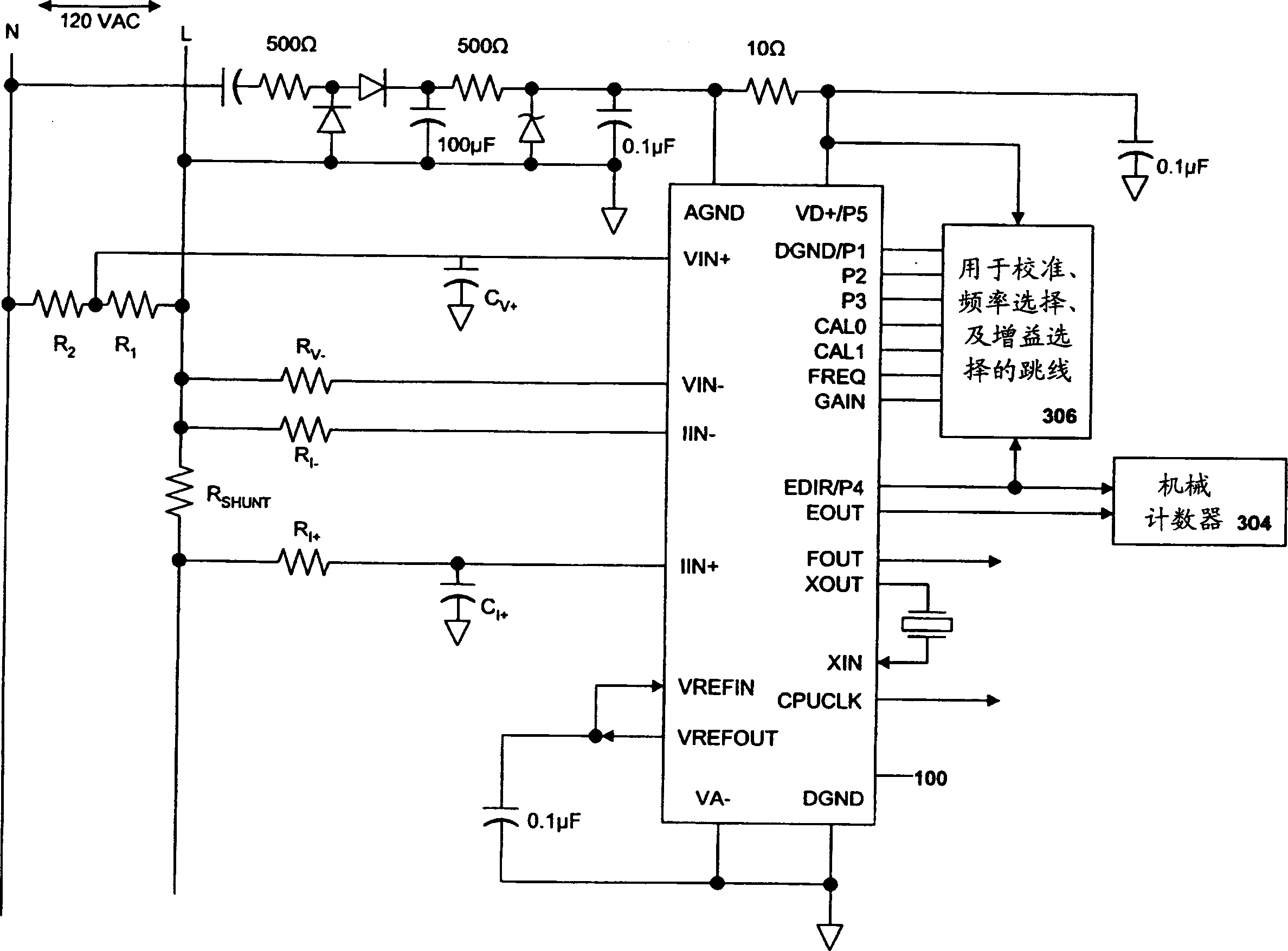

[0034] image 3An integrated circuit 100 of the present invention (an exemplary CS5462) is shown mounted to a system board 300 . The system board 300 is connected to a single phase, two wire branch line 302 and various system board components are connected to the chip 100 for measuring the power used. Power is tracked and read by a mechanical counter 304 . Configuration pins 224-228 are connected to program select pins P1-P5 214-222 via jumpers 306 on system board 300.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com