Flash memory unit, flash memory unit array and mfg. method thereof

A memory cell array and memory cell technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of slow operation speed of memory cells, small reading current of memory cells, and inability to improve device performance, etc. , to achieve the effect of improving operation speed and performance, improving gate coupling rate, and high electron injection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

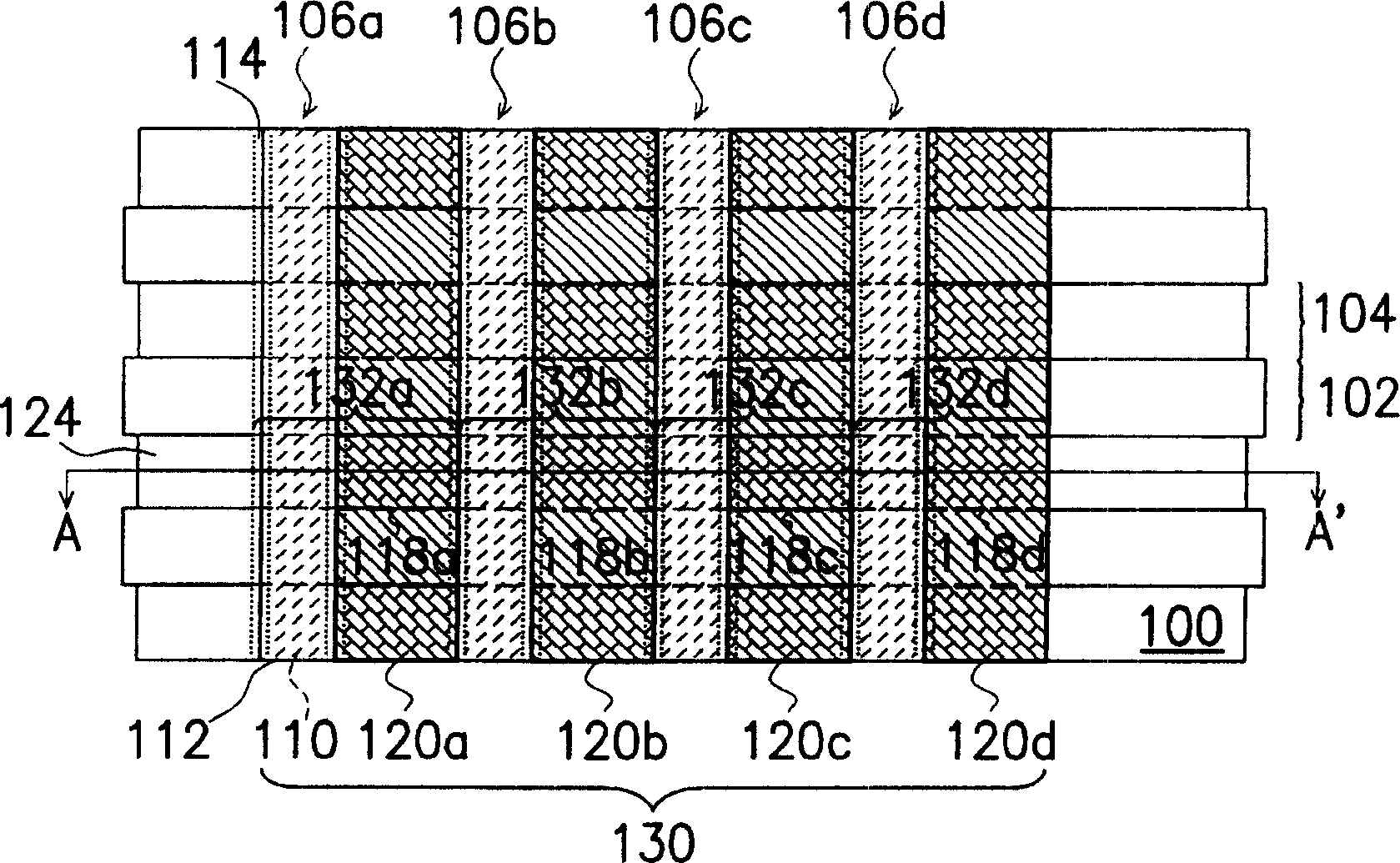

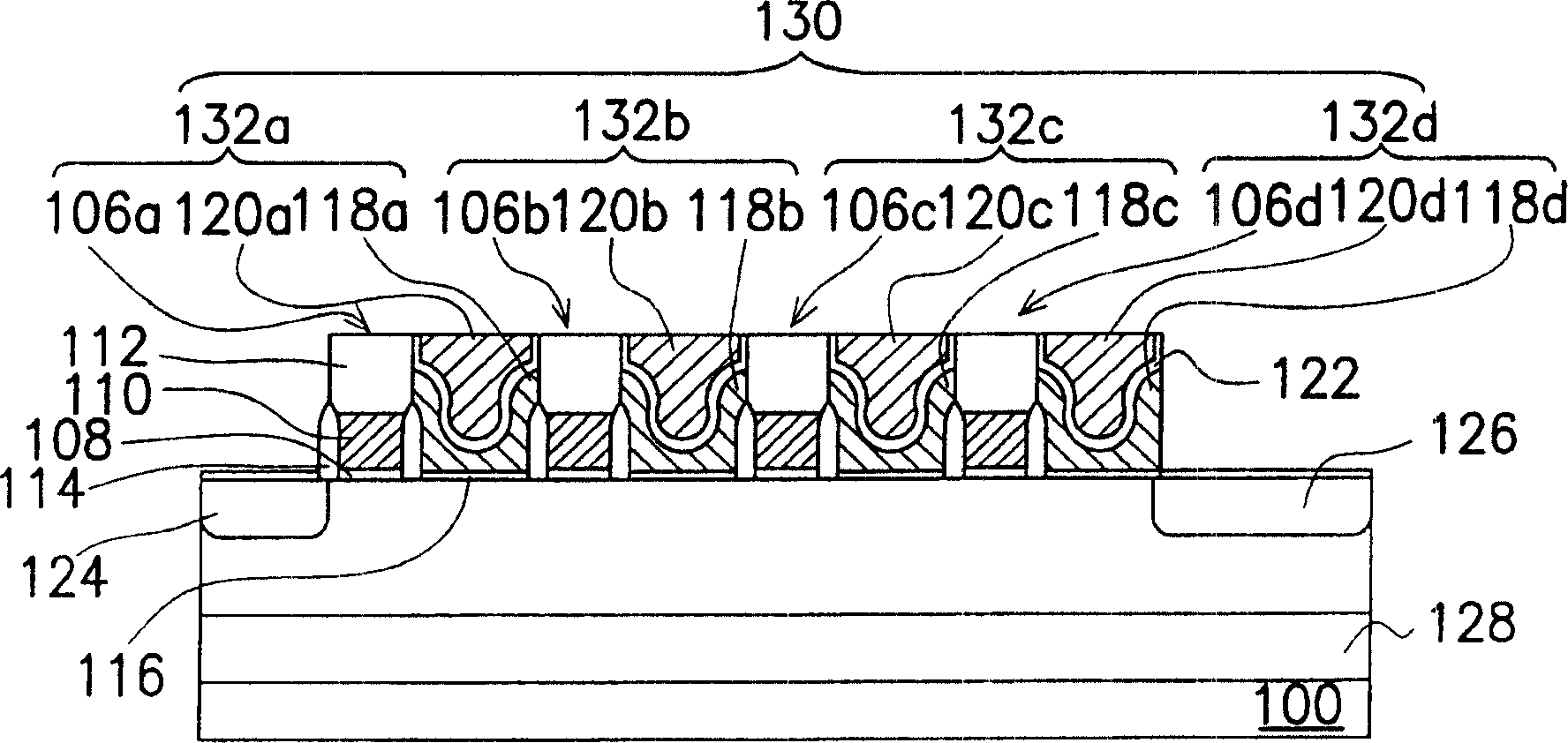

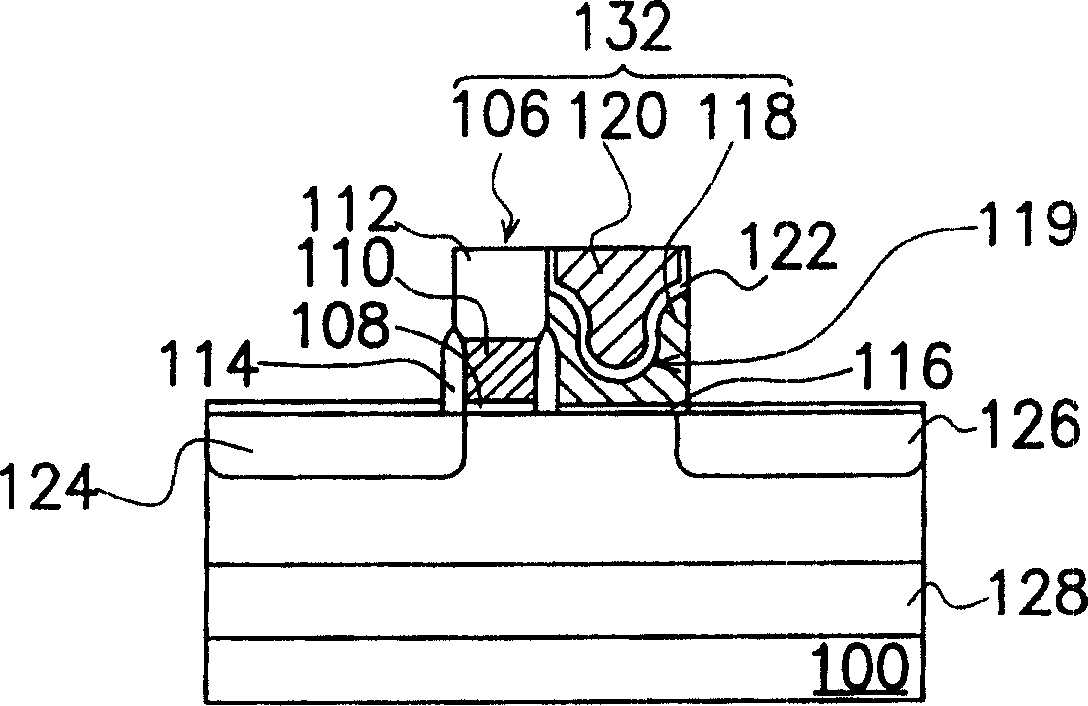

[0048] Figure 1A To show the top view of the NAND type flash memory cell array of the present invention. Figure 1B For display Figure 1A A cross-sectional view of the structure along the line A-A' in the middle.

[0049] Please also refer to Figure 1A versus Figure 1B , The flash memory cell array structure of the present invention is at least composed of a substrate 100, an element isolation structure 102, an active area 104, a plurality of stacked gate structures 106a-106d (each stacked gate structure 106a-106d starts from the substrate 100). The sequence is a select gate dielectric layer 108, a select gate 110, a cap layer 112), a spacer 114, a tunneling dielectric layer 116, a plurality of floating gates 118a-118d, and a plurality of control gates 120a- 120d, the inter-gate dielectric layer 122, the drain region 124, and the source region 126 are formed.

[0050] The substrate 100 is, for example, a P-type silicon substrate, and the substrate 100 is provided with a deep ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com