Complementary semiconductor and assembling element thereof

A technology of combining components and semiconductors, applied in the direction of transistors, etc., can solve problems such as insufficient space, and achieve the effects of solving insufficient space, improving resolution, and reducing width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

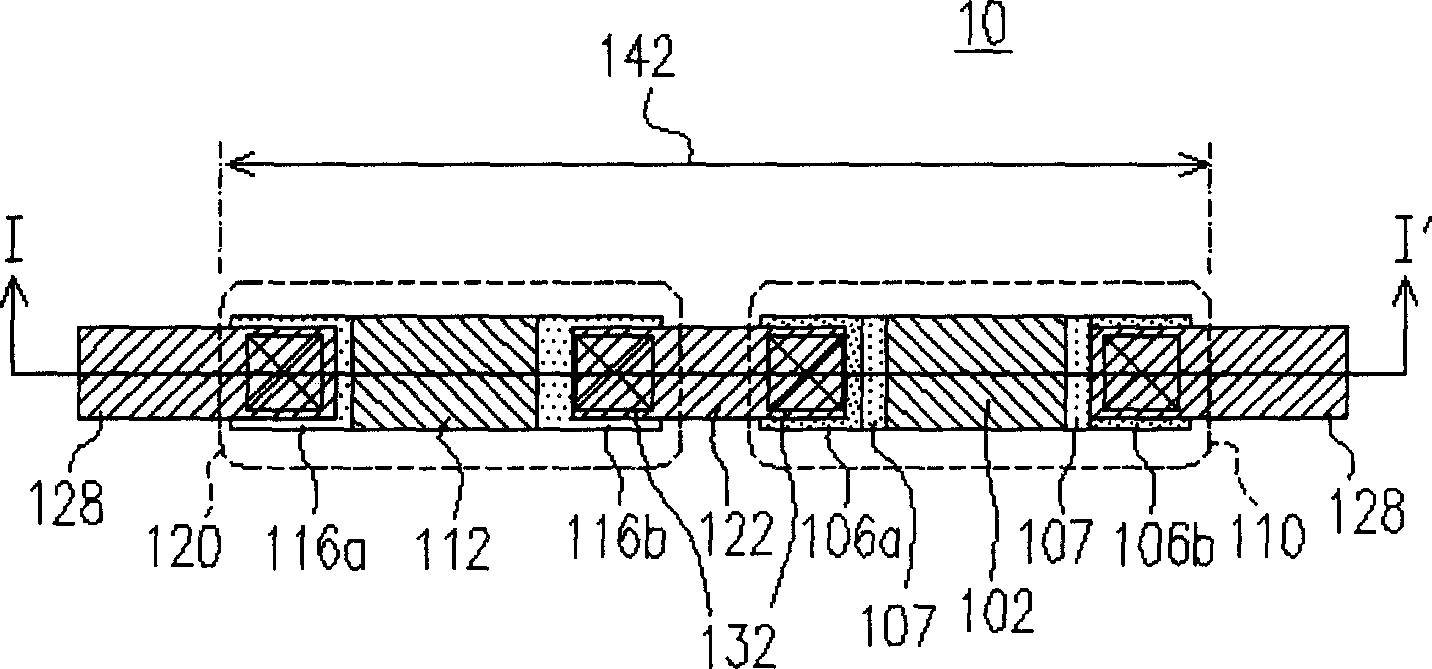

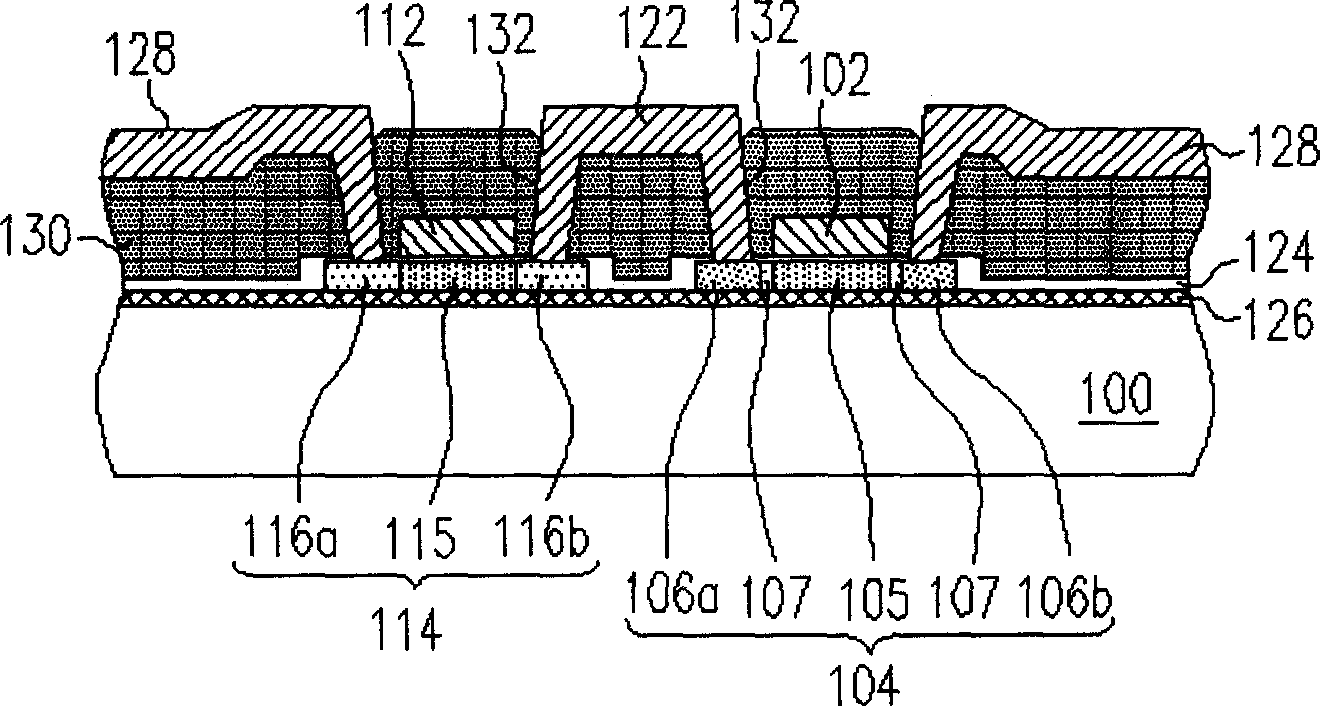

[0046] The present invention can be applied to low temperature polysilicon (low temperature poly-Si, LTPS for short) thin film transistor (thin film transistor, TFT for short), please refer to Figure 2A and Figure 2B .

[0047] Figure 2A is a schematic top view of a complementary metal oxide semiconductor (CMOS) according to a first embodiment of the present invention, and Figure 2B is based on Figure 2A The cross-sectional schematic diagram of the II-II' section.

[0048] Please refer to Figure 2A and Figure 2B , the complementary metal oxide semiconductor 20 of the present invention includes an N-type low-temperature polysilicon thin film transistor 210 and a P-type low-temperature polysilicon thin-film transistor 220 located on a substrate 200, and an interlayer dielectric layer is covered on the low-temperature polysilicon thin-film transistor 210 and 220 (inter-layer dielectrics, ILD for short) 230. In this embodiment, the N-type low-temperature polysilicon ...

no. 2 example

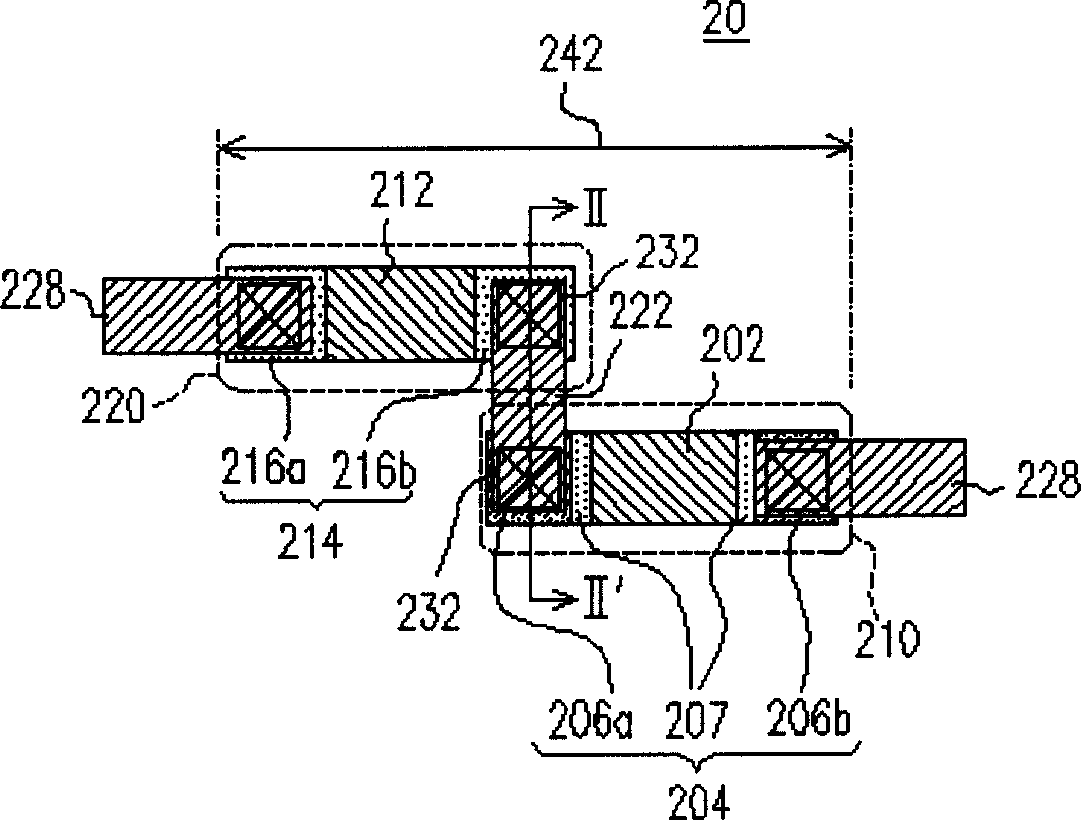

[0054] Any circuit structure composed of at least one P-type thin film transistor and at least one N-type thin film transistor can be laid out by using the present invention, please refer to image 3 .

[0055] image 3 It is a schematic top view of a CMOS composite device according to a second embodiment of the present invention. Please refer to image 3 , the combined element 30 of the present invention includes an N-type low-temperature polysilicon thin film transistor 310 and two P-type low-temperature polysilicon thin film transistors 320 . Although there are only three thin film transistors in this embodiment, it is not limited to the application of the present invention, but only used as an example, so as long as the design is according to the characteristics of the present invention, no matter how many thin film transistors are available.

[0056] Please continue to refer to image 3 , the N-type low-temperature polysilicon thin film transistor 310 of this embodime...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com