Information processor and memory access arranging method

An information processing device and memory technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve the problems of external access speed reduction and final set operation speed reduction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

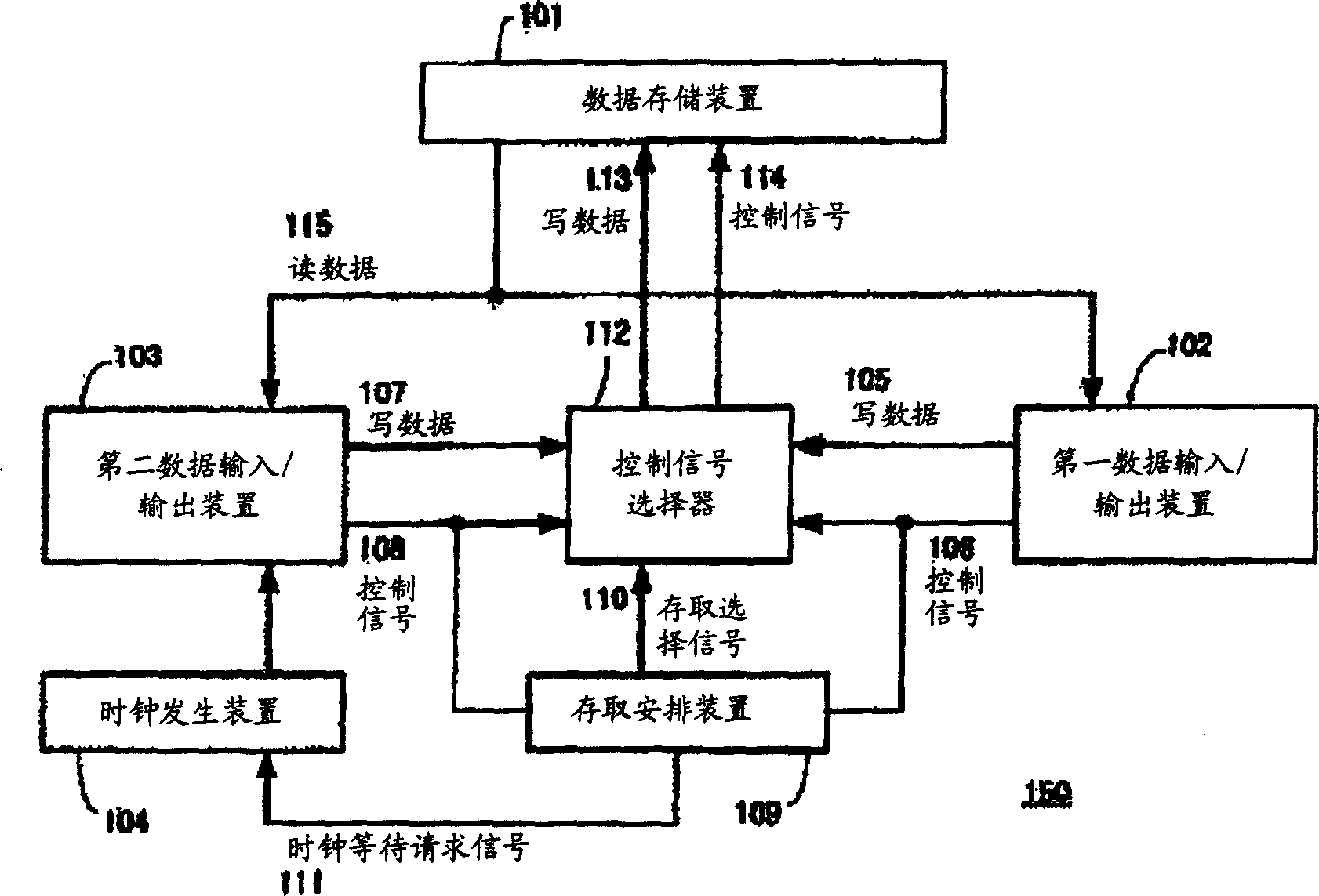

[0032] attached figure 1 is a block diagram showing the structure of an information processing apparatus according to a first embodiment of the present invention. in the attached figure 1 , the information processing device 150 includes a data storage device 101, a first data input / output device 102, which has a high access priority to the data storage device 101, and a second data input / output device 103, which has a low access priority, The clock generating means 104 is used to provide a clock to the second data input / output means 103 , the access arrangement means 109 , and the control signal selector 112 .

[0033] The access arrangement device 109 monitors the control signal 106 of the first data input / output device 102 and the control signal 108 of the second data input / output device 103, and generates an access selection signal 110 for use in the first data input / output device Switching between 102 and the second data input / output device 103 will provide both control ...

no. 2 example

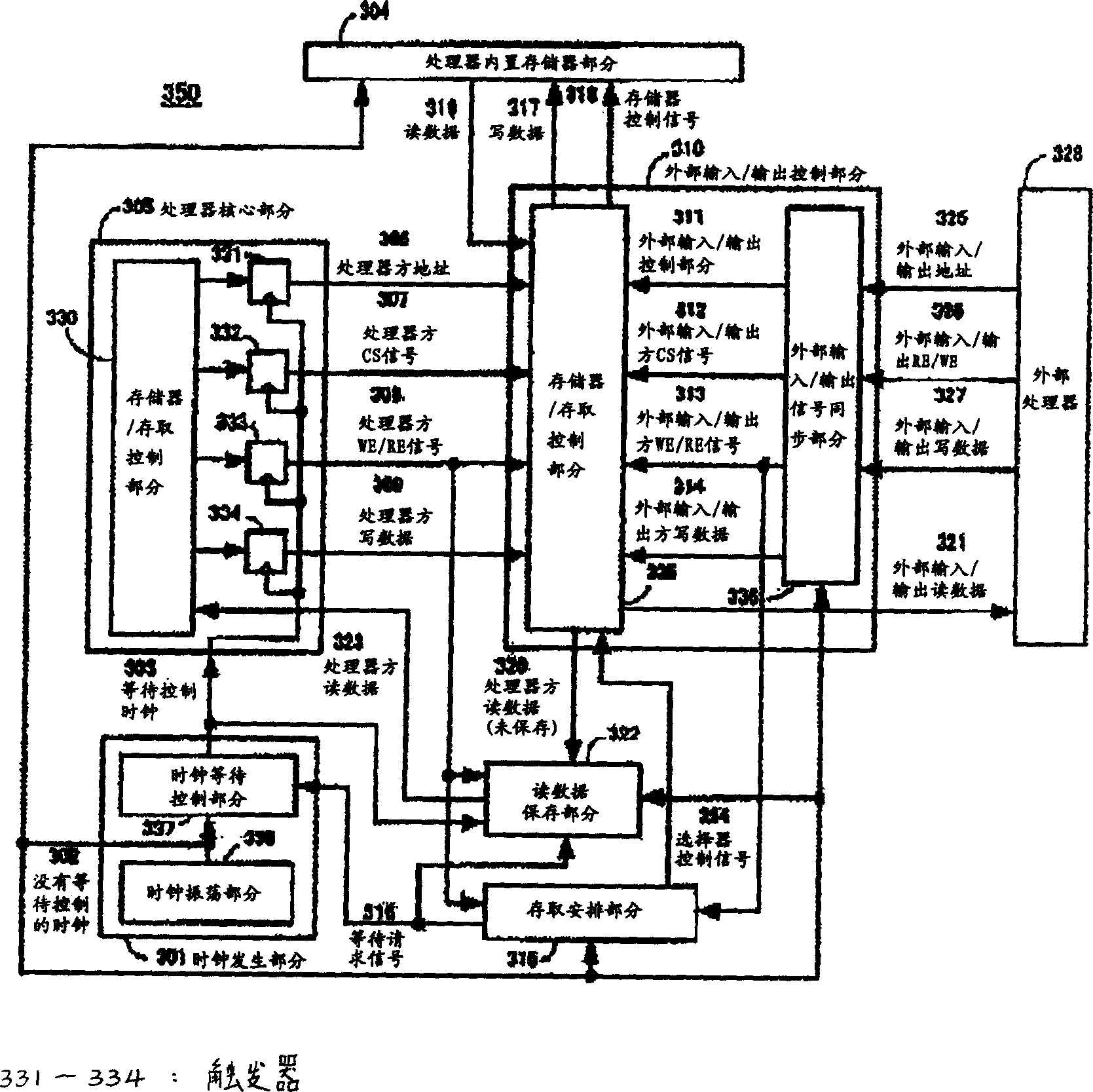

[0042] attached image 3 is a block diagram showing a schematic configuration of an information processing apparatus according to a second embodiment of the present invention. in the attached image 3 , an information processing apparatus 350 includes a clock generation section 301, a processor built-in memory section 304 provided in the processor and accessible from outside the processor, a processor core section 305 for performing pipeline processing by instructions, an external input The / output control section 310, which has a higher access priority than the access priority of the processor core section 305 to the processor built-in memory 304, reads the data storage section 322 for saving the output from the external input / output control section 310 The processor side read data 320 and the access scheduling part 315 are used to generate the wait request signal 316 when the processor core part 305 and the external input / output control part 310 access simultaneously.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com