Fuse wire possessing cover layer and forming method

A covering layer and fuse technology, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as difficulty in controlling the etched depth of the fuse window 107b, failure of the fuse 107b to be pierced, and loss of function.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

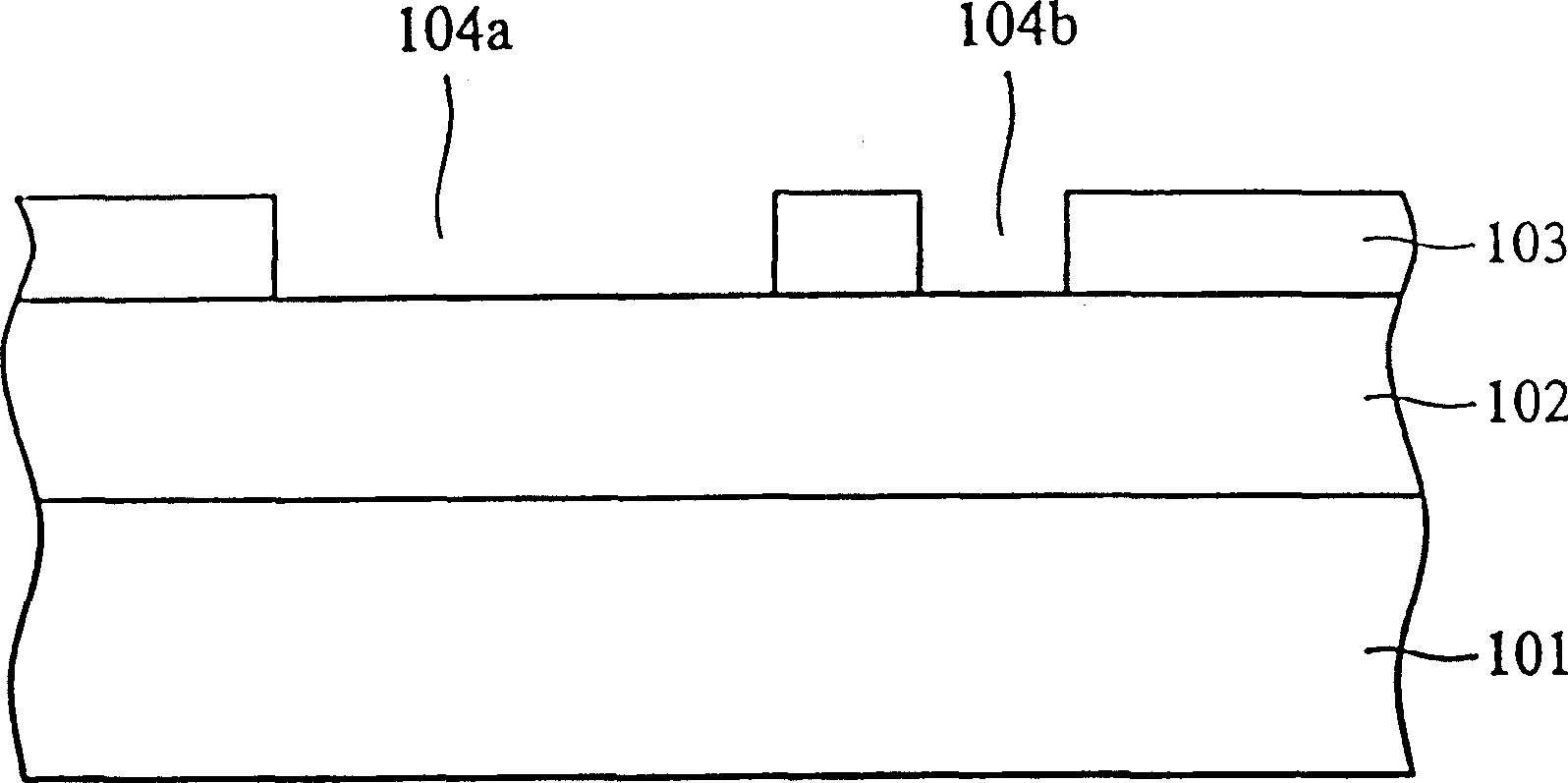

[0048] Please refer to Figure 2a Firstly, a semiconductor substrate 201 is provided, and any required elements can be formed on the semiconductor substrate 201 . A dielectric layer 202 and a patterned mask layer 203 are sequentially formed on the semiconductor substrate 201, the patterned mask layer 203 has openings 204a and 204b, the openings 204a and 204b will expose part of the surface of the dielectric layer 202, and The position of the opening 204a is the position of the subsequent formation of the metal interconnection, and the position of the opening 204b is the position of the subsequent formation of the fuse. Wherein, the semiconductor substrate 201 is, for example, silicon crystal; the dielectric layer 202 is, for example, a silicon oxide layer.

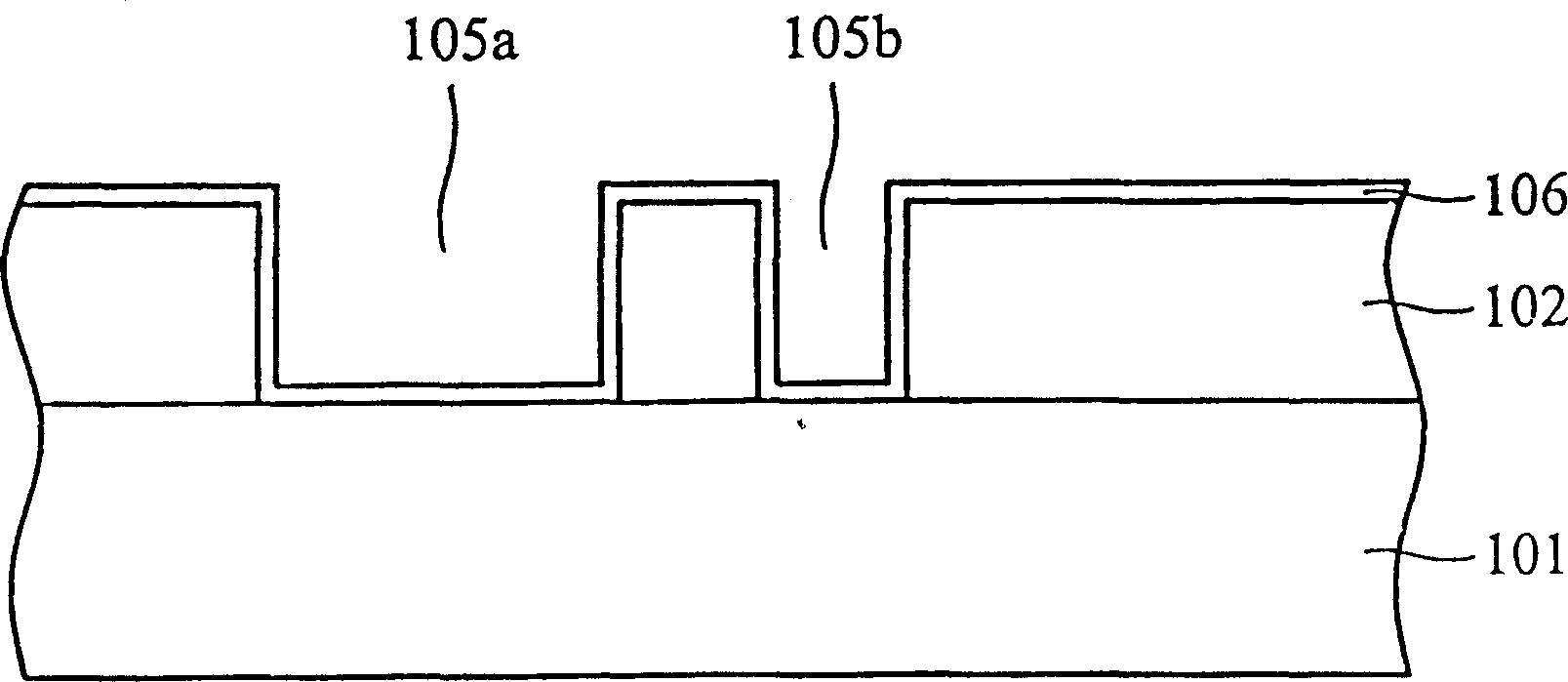

[0049] Please refer to Figure 2b , using the patterned mask layer 203 as a mask to etch the dielectric layer 202 to form openings 205 a and 205 b on the dielectric layer 202 , the openings 205 a and 205 b will expose pa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com