Stack speed process method in Ethernet exchanger

A processing method and switch technology, applied in the field of electrical communication, can solve the problems of reducing stack forwarding performance, large forwarding delay, complex design, etc., and achieve the effects of shortening forwarding delay, good compatibility, and improving practicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

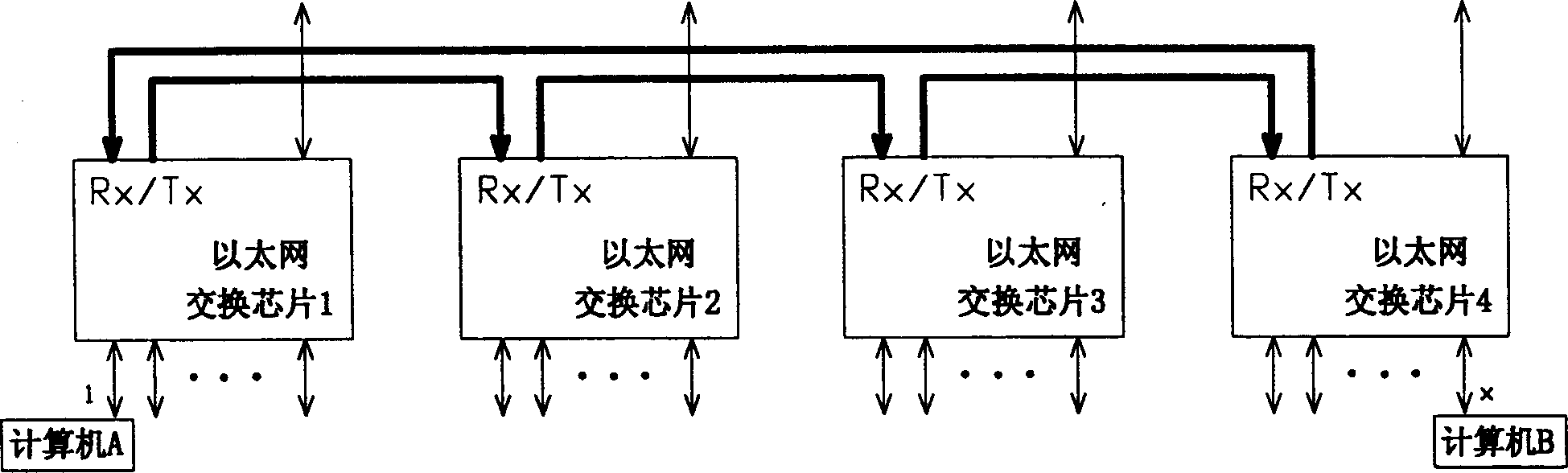

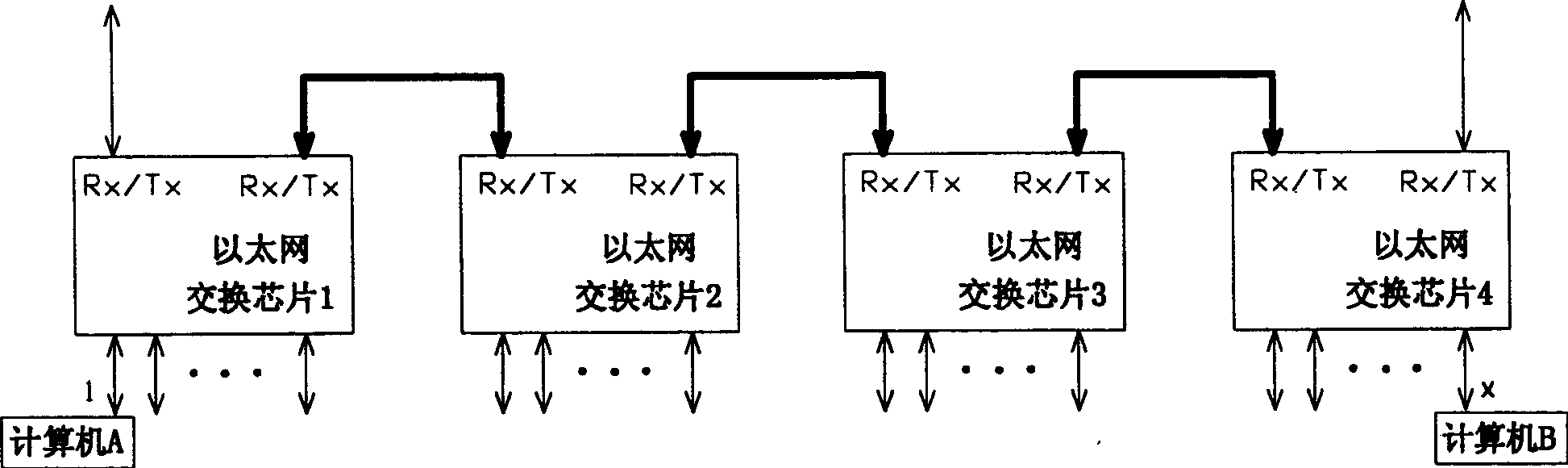

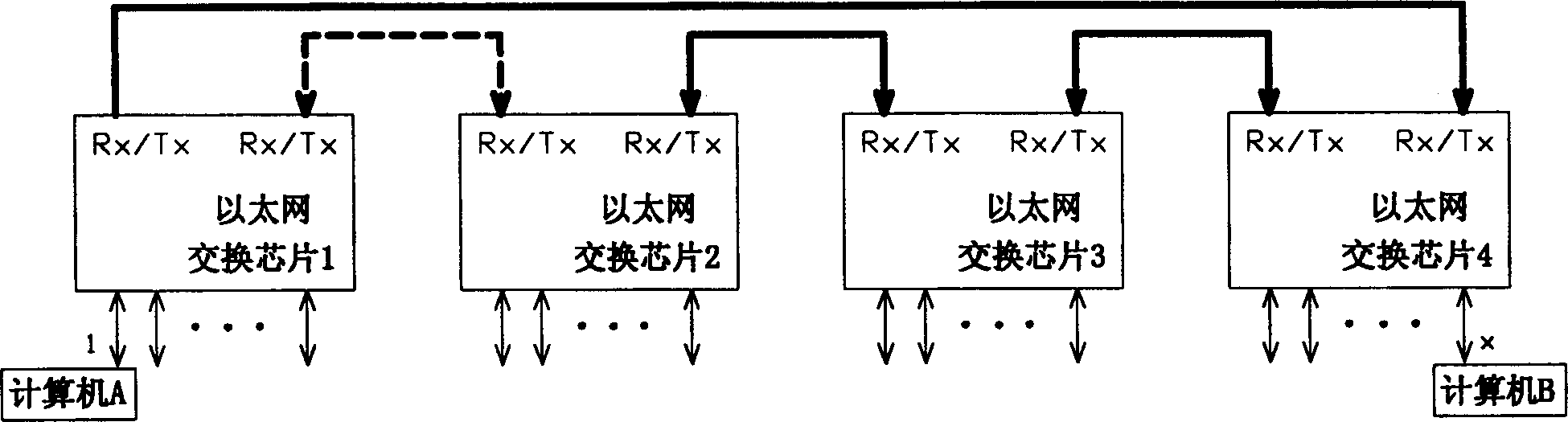

[0032] Below according to accompanying drawing and embodiment the present invention will be described in further detail:

[0033] Switching chip forwarding and processing flow of the present invention are as follows: as Figure 5 As shown, in the stack link formed by the switch chip, the normal forwarding process of the data frame received by the switch chip is as follows: a. Receive the data frame; b. Protocol processing of the frame and forwarding search of the destination port of the frame; c. Judgment Whether the destination port is a local port, if the destination port is a local port, it will be sent to the destination port of the frame through process d. Before the process b, a stacking processing branch 2 is set to judge whether the source port of the data frame is a stacking port , for the data frame whose source port is determined to be a stack port, it is judged whether the current chip is the end of the stack link. If the current chip is not the end of the stack li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com