Multichannel FILO data buffer storage devices

A first-in, first-out, data buffering technology, applied in memory systems, electrical digital data processing, memory address/allocation/relocation, etc., can solve the problems of consuming combinational logic resources, difficulty in FIFO stacking, consuming data counters, etc., to simplify Complexity, resource savings, effect of resource reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

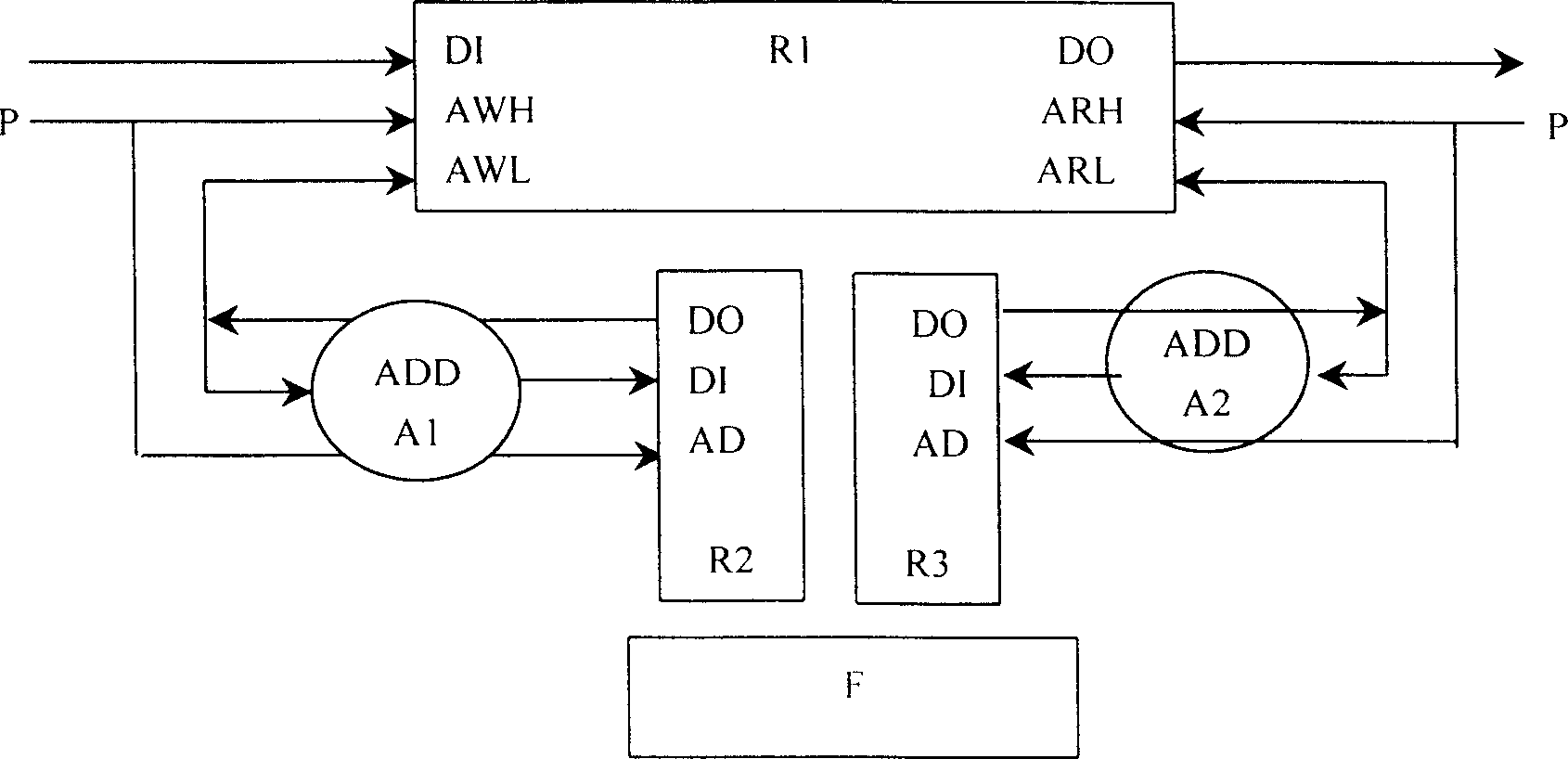

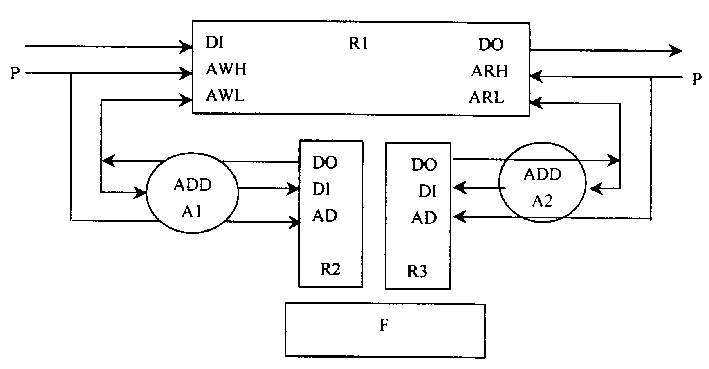

[0014] figure 2 It is an internal block diagram of a specific example of the multi-channel FIFO data buffering device of the present invention. like figure 2 As shown, the data storage unit includes a dual-port RAM R1 for data buffering of multiple channels, the address resources of the RAM R1 are redistributed, and the channels are divided into blocks for access, and the interior of each block can be regarded as a corresponding The channel's FIFO.

[0015] The read / write pointer control unit is composed of at least one adder A1 / A2 and a single-port RAM R2 / R3. The address of the single-port RAM R2 / R3 of the read / write pointer control unit is also divided by channels, and the R2 / R3 address corresponding to a certain channel is stored with the next read / write in the R1 block corresponding to the channel. The offset of the operation position. After each read / write operation, use the read / write adder A1 / A2 to add one to the current offset and store it in the R2 / R3 unit corre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com