Delay phase-locking loop unit and its clock signal generating method

A technology of delay-locked loop and clock signal, which is applied to the automatic control of power and electrical components, etc. It can solve the problems of data reception error at the receiving end, signal delay accuracy and insufficient transmission rate, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

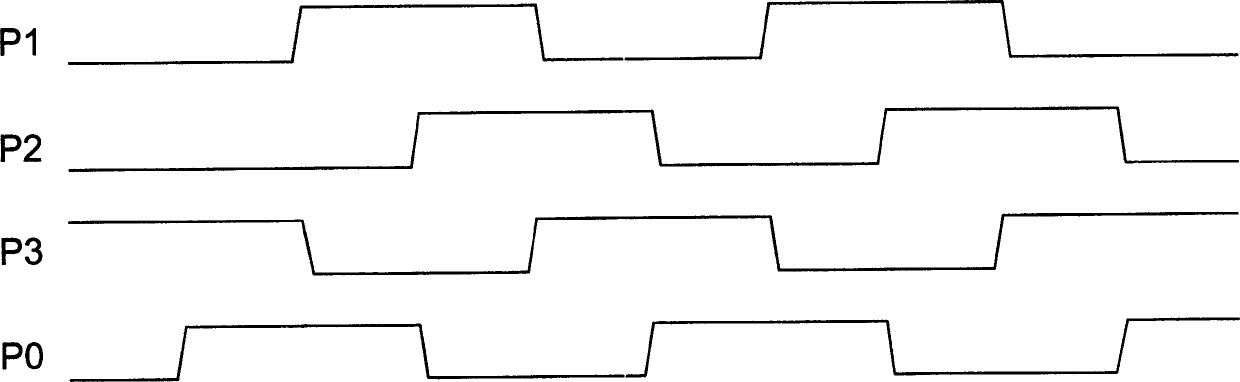

[0028] Please refer to FIG. 3 , which is a schematic block diagram of a preferred embodiment of the present invention developed to improve common defects. The improved delay-locked loop device (Delay-Locked Loop, DLL) also receives a reference clock signal CLK and sends it to into a controlled delay circuit 31 for phase delay processing. The controlled delay circuit 31 is also formed by connecting four controlled delay lines (delay lines) 311, 312, 313, 314, and each controlled delay line is mainly composed of several delay units (delay units) ( not shown in the figure). After the reference clock signal CLK passes through the four controlled delay lines 311 , 312 , 313 , and 314 , it can basically generate four output clock signals P1 , P2 , P3 , and P0 with different phases.

[0029] Similarly, in order to keep the state in phase with the reference clock signal CLK, the output clock signal P0 and the reference clock signal CLK are simultaneously input to a phase detector 32 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com