Circuit for recovering timing data and implementing method

A clock data recovery and circuit technology, applied in electrical components, digital transmission systems, transmission systems, etc., can solve the problems of different implementation methods and poor anti-jitter ability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be described in further detail below in conjunction with the accompanying drawings.

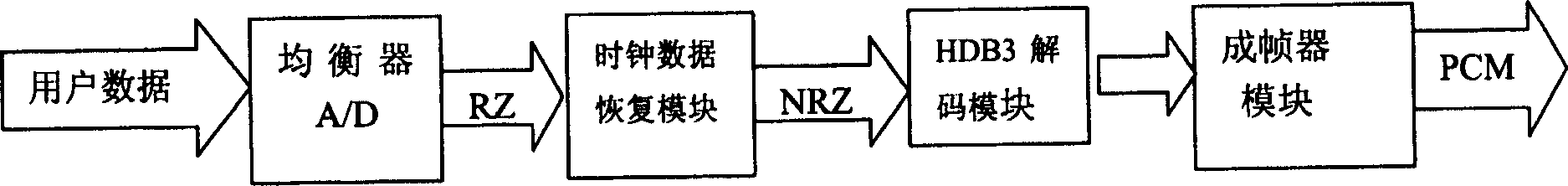

[0025] figure 1 The position of the clock data recovery module in the whole data processing system is described. The position of the clock data recovery module in the E1 system can be seen from the attached figure. The user data is outputted to the clock data recovery module after the balanced analog-to-digital conversion. The RZ signal recovers the system clock RCLK of the entire module after passing through the clock data recovery circuit. and the data NRZ signal to be further processed.

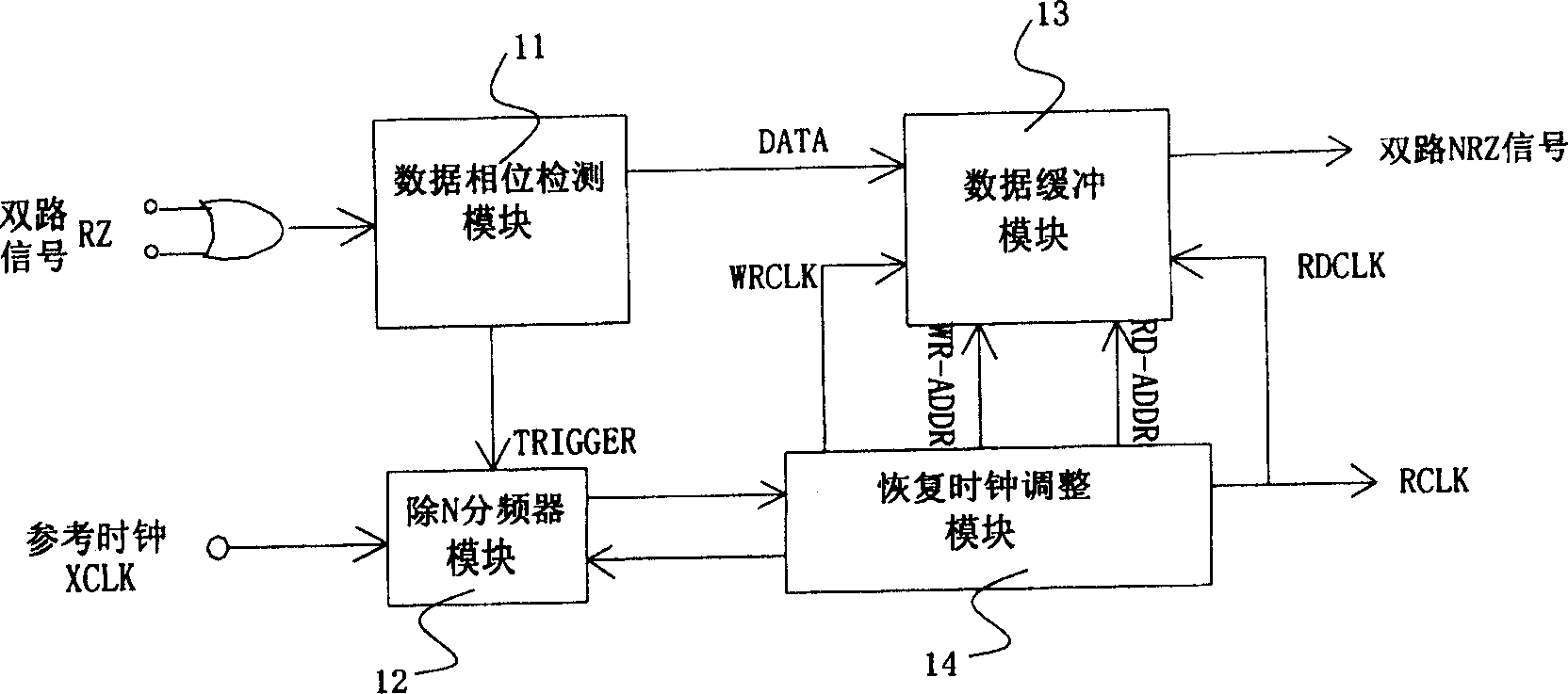

[0026] image 3 It is a system structure diagram of the clock data recovery circuit of the present invention. It includes four parts: data detection module 11 , N frequency division counter module 12 , data buffer module 13 and clock adjustment module 14 . In order to improve the sensitivity of the clock adjustment, smooth the small clock jitter, and recover the 2.04...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com