Method for forming integrated circuit

A technology of integrated circuits and conductive layers, applied in circuits, electrical components, electrical solid devices, etc., can solve problems such as harmful effects of fuse windows

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

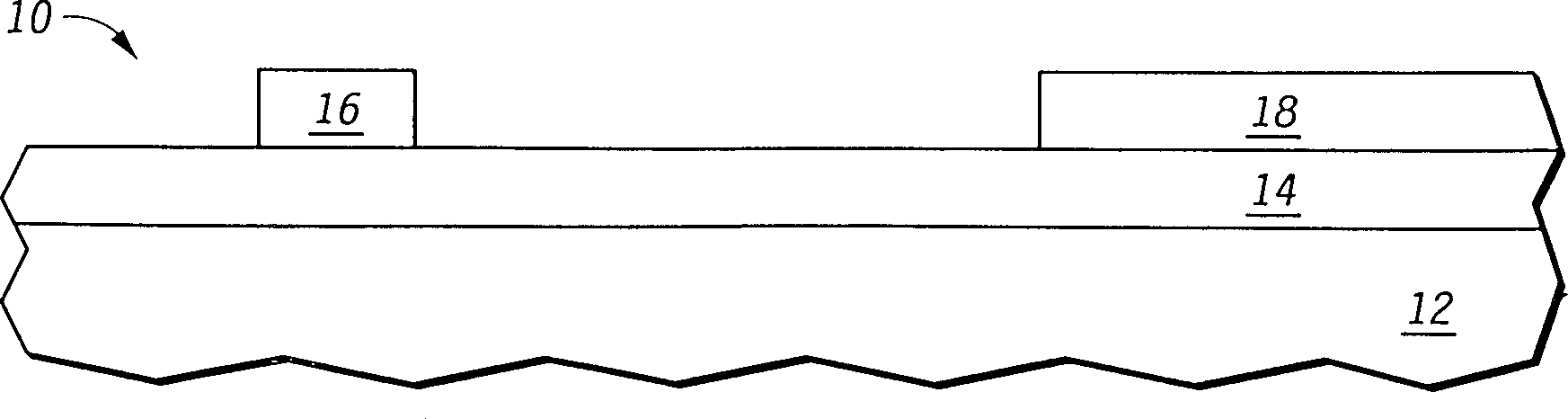

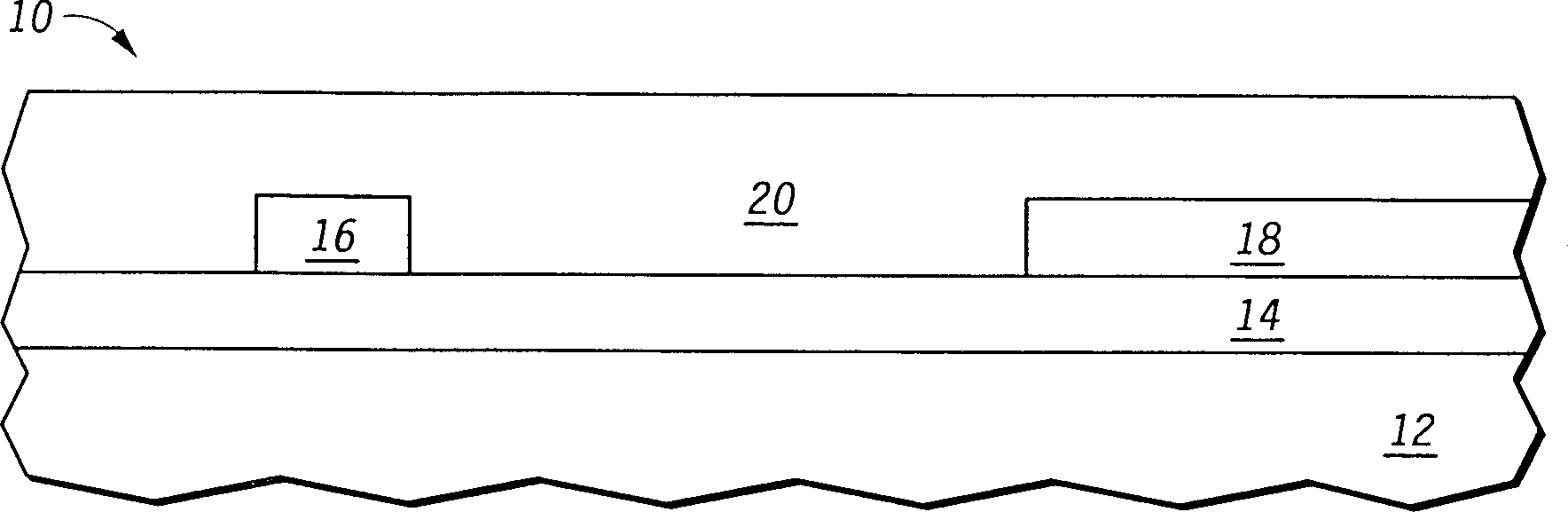

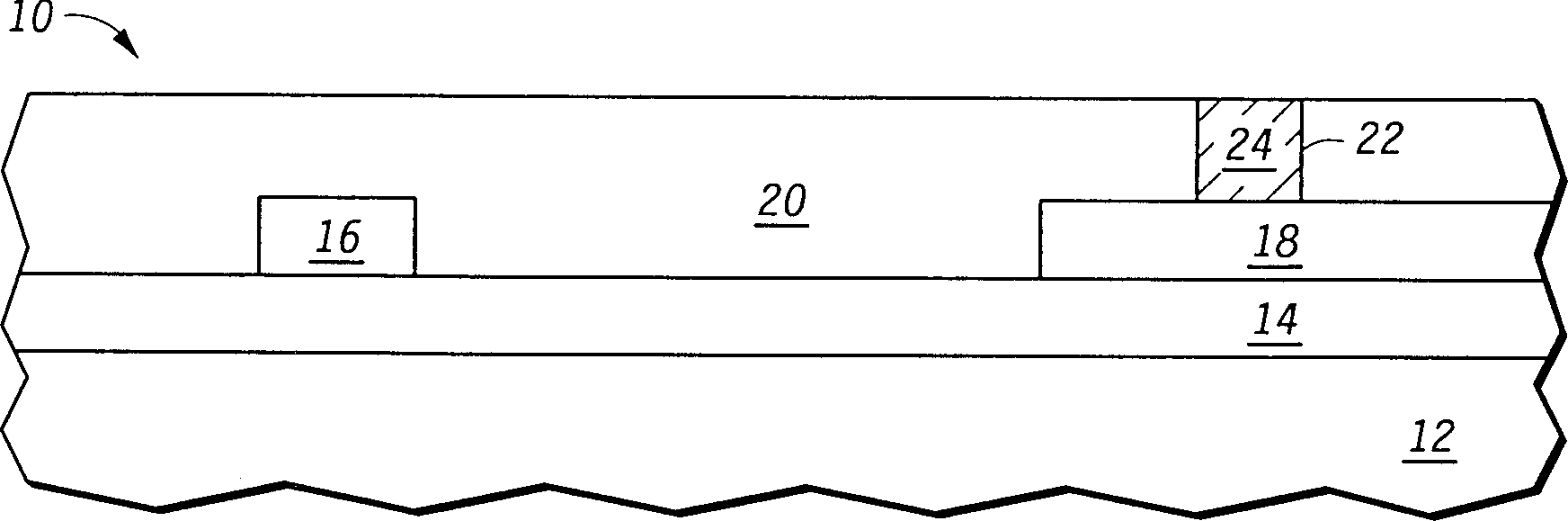

[0008] Figure 1-7 Cross-sectional views illustrating process steps of forming an integrated circuit in accordance with one embodiment of the present invention. figure 1 is a portion 10 of an integrated circuit structure that includes a semiconductor substrate 12 , a dielectric layer 14 , fuses 16 , and conductive interconnects 18 . In one embodiment, semiconductor substrate 12 is a single crystal silicon substrate. In addition, the semiconductor substrate 12 may also be a silicon-on-insulator substrate, a silicon-on-sapphire substrate, or the like.

[0009] In one embodiment, the dielectric layer 14 is a plasma deposited oxide layer formed using tetraethyl orthosilicate (TEOS) as a gas source. In addition, the dielectric layer 14 can be a silicon nitride layer, a phosphosilicate glass (PSG) layer, a borophosphosilicate glass (BPSG) layer, a spin-on glass (SOG) layer, a silicon oxynitride layer, a polyimide layer, a low dielectric Electrical constant insulators, or a combin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com