Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing the performance of the LDMOS device 100, reducing the breakdown voltage, easily accumulating charges, etc., and achieving the effect of ensuring the breakdown protection. , Ensure the uniformity of thickness and reduce the effect of sharp corners

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0032] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

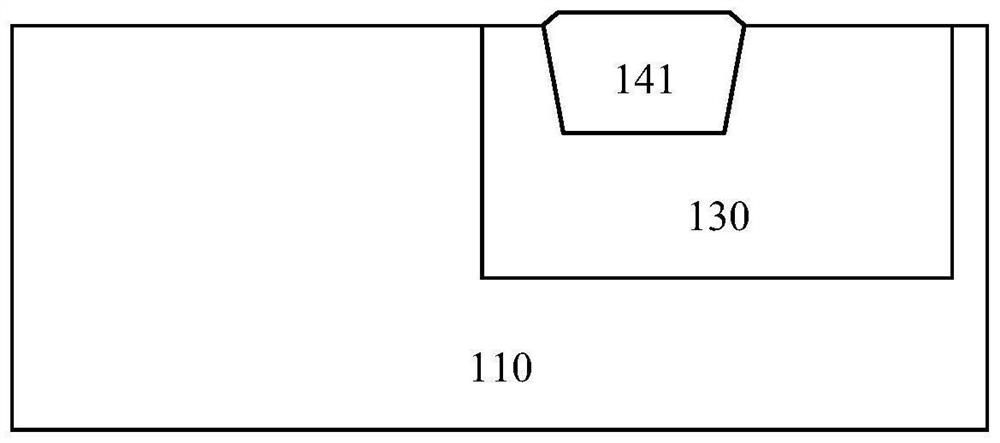

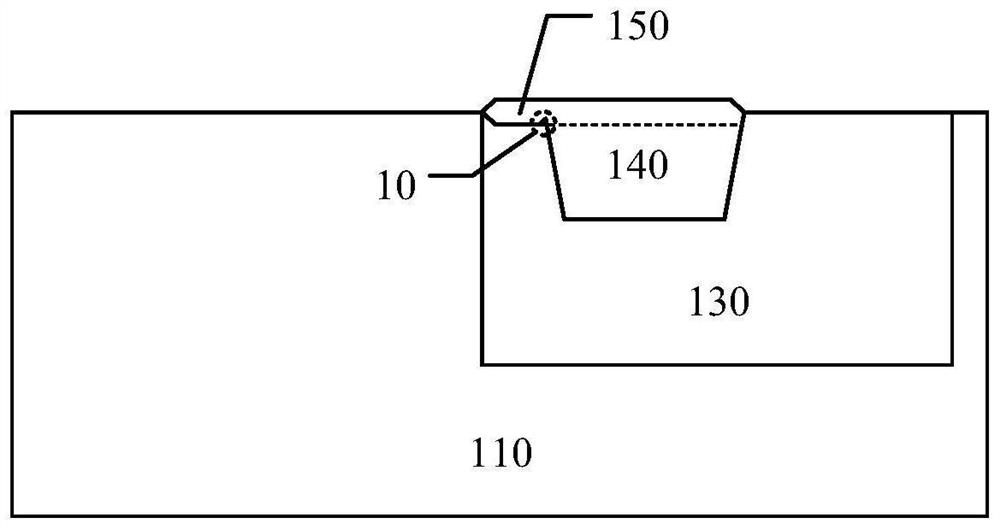

[0033] Figure 2A to Figure 2C A partial process schematic diagram of a manufacturing method of an LDMOS device according to the prior art is shown.

[0034] refer to Figure 2A , in the prior art, a groove is etched at the position of the shallow trench isolation region, and oxide is deposited in the groove to obtain a vertical oxide layer structure 141. In order to ensure the isolation effect, the vertical oxide layer structure 141 The height exceeds the upper surface of the semiconductor sub...

PUM

| Property | Measurement | Unit |

|---|---|---|

| angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com