Phase unwrapping algorithm based on double counters

A phase unwrapping, double counter technology, applied in the field of signal processing, to achieve the effect of improving real-time performance and solving slow calculation speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

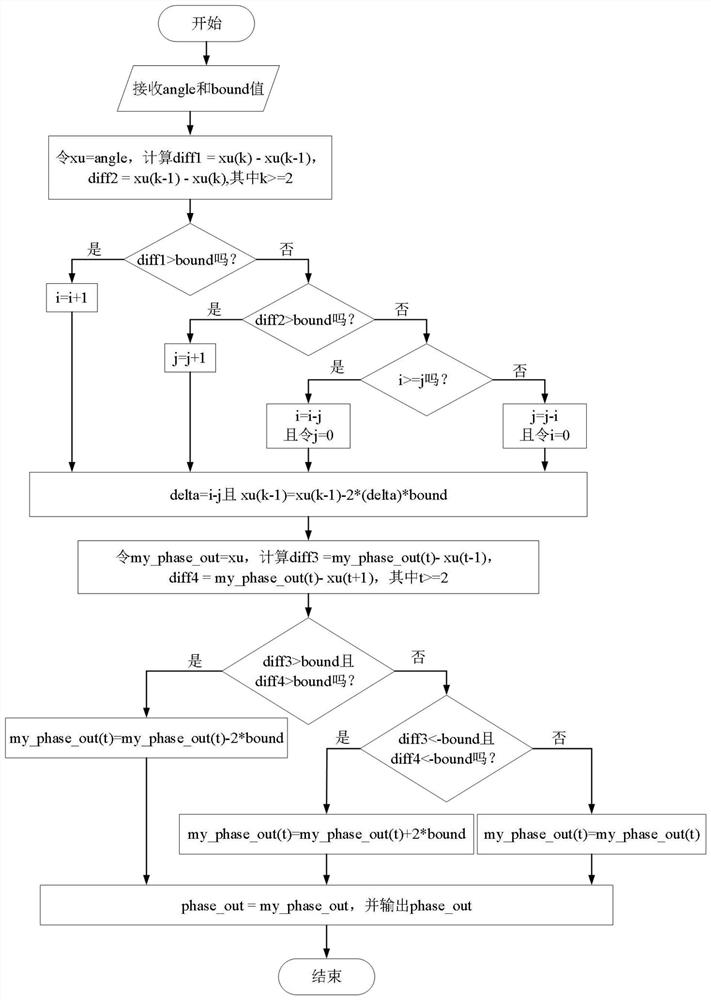

Method used

Image

Examples

Embodiment 1

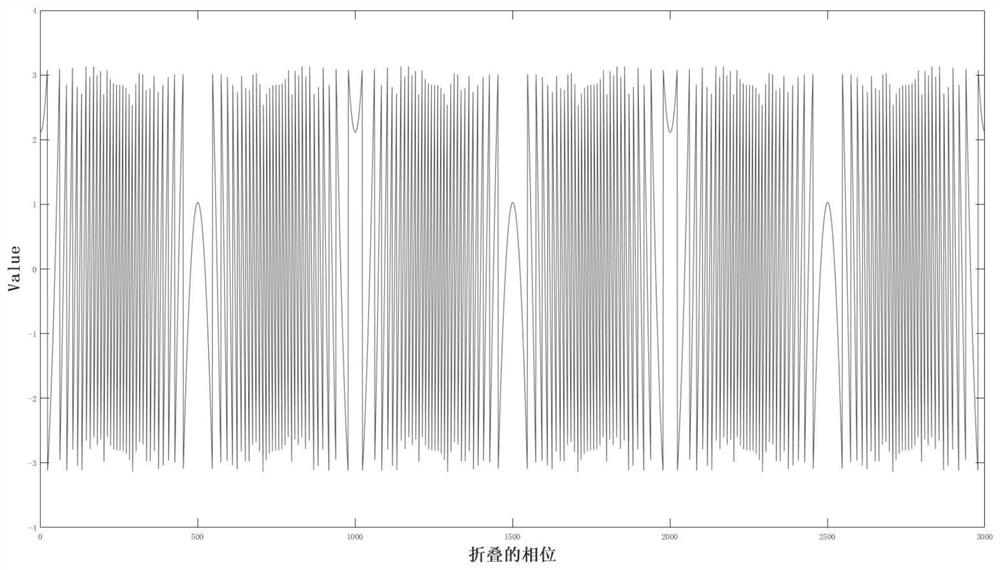

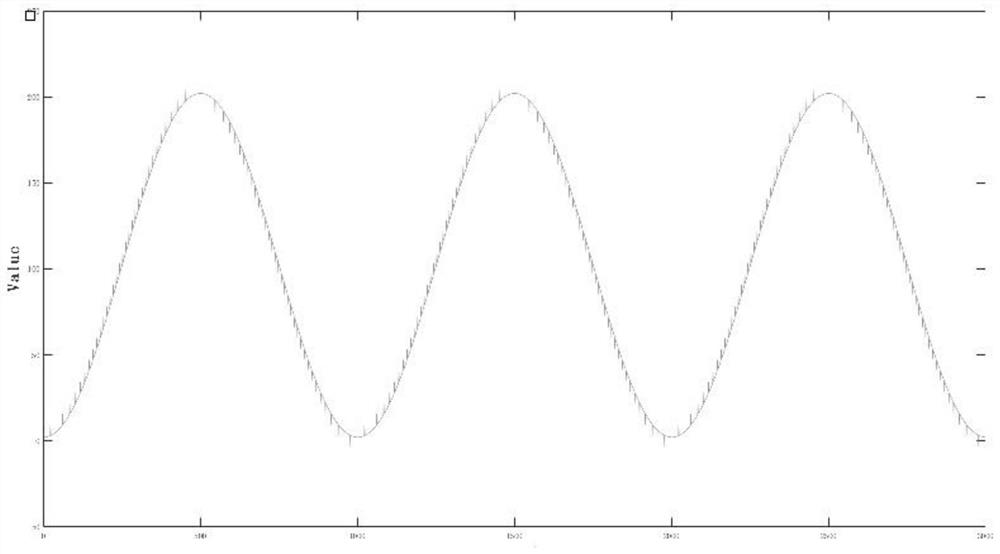

[0071] This algorithm is also applicable to two-dimensional expansion problems, such as Image 6 As shown, the original 3D graph constructed in MATLAB adds noise to the original 3D graph as Figure 7 As shown, the corresponding two-dimensional grayscale image containing noise is obtained as Figure 8 As shown, the three-dimensional phase folding diagram obtained by the arc tangent of the above three-dimensional image is as follows Figure 9 As shown, the two-dimensional diagram of the obtained phase folding is shown as Figure 10 As shown, the above phase unwrapping algorithm is applied to phase unwrap the rows and columns of the two-dimensional image, and the obtained three-dimensional image is as follows Figure 11 As shown, the original image can be restored by separately processing the data at the edge of the three-dimensional image.

Embodiment 2

[0073] This algorithm transforms the one-dimensional phase unwrapping algorithm on the software platform to be suitable for the FPGA platform. Part of the Verilog code is attached below for illustration:

[0074]

[0075]

[0076]

[0077]

[0078] The above is a Verilog code fragment, which specifically describes the core code implemented on the FPGA. The above pi is the fixed-point constant corresponding to pi; M, N, O, P, Q, and L are the digits of the corresponding variables. The sizes of M, N, O, P, Q, and L can be modified according to requirements.

[0079] The above clk is the system clock, unwrap_fig is valid when the reset signal is 0, dout_last_reg1 is valid when the data valid signal is 1, pi_2 is a constant corresponding to the fixed-point number of 2π, pi_2n is the fixed-point number corresponding to 2π*delta, and phase_reg1 is the truncated phase The result of one beat, phase_reg is the truncated phase, phase_reg2 is the result of two beats of the tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com