Calibration method and system for current density over-standard region of integrated circuit layout

A current density and integrated circuit technology, which is applied in the field of calibration in areas where the current density of the integrated circuit layout exceeds the standard, can solve the problems of inability to accurately obtain useful information, complicated shape of the integrated circuit layout, and calibration methods that are no longer valid.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0089] The application will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solutions of the present invention more clearly, but not to limit the protection scope of the present application.

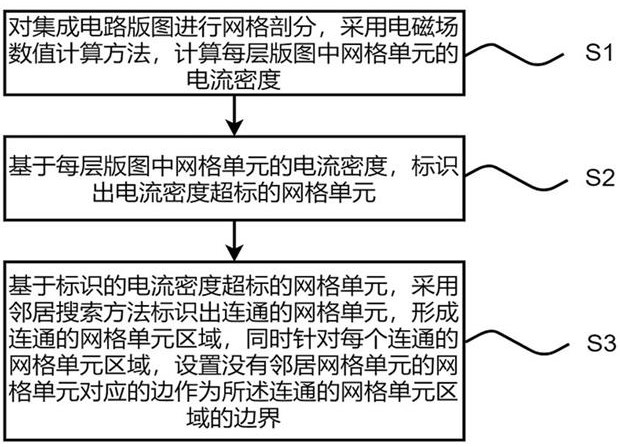

[0090] In the first aspect, this application proposes a method for calibrating the region where the current density of the integrated circuit layout exceeds the standard, such as figure 1 shown, including the following steps:

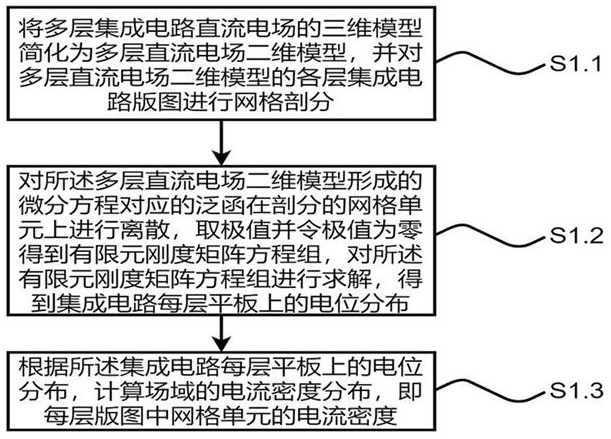

[0091] Step S1: performing grid division on the layout of the integrated circuit, and calculating the current density of the grid cells in each layout layer by using the electromagnetic field numerical calculation method;

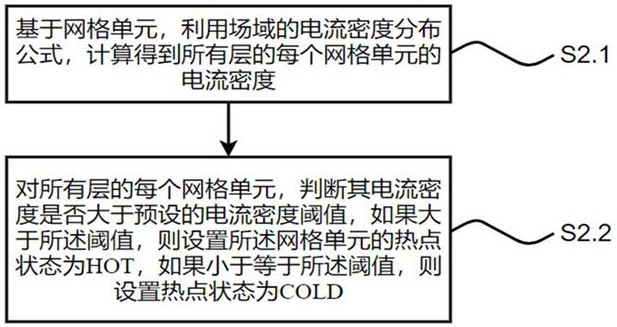

[0092] Step S2: Based on the current density of the grid cells in each layout layer, identify the grid cells whose current density exceeds the standard;

[0093] Step S3: Based on the grid cells whose identified current density exceeds the standard, us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com