DAC capacitor array, SAR type analog-to-digital converter and analog-to-digital conversion method

A capacitor array and capacitor technology, used in DAC capacitor arrays, SAR type analog-to-digital converters, and analog-to-digital conversion fields, can solve the problems of large RC time constant, long capacitor voltage settling time, limiting ADC quantization speed, etc., to improve quantization. Speed, effect of saving voltage settling time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The specific implementation manners of the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific implementation manners described here are only used to illustrate and explain the embodiments of the present invention, and are not intended to limit the embodiments of the present invention.

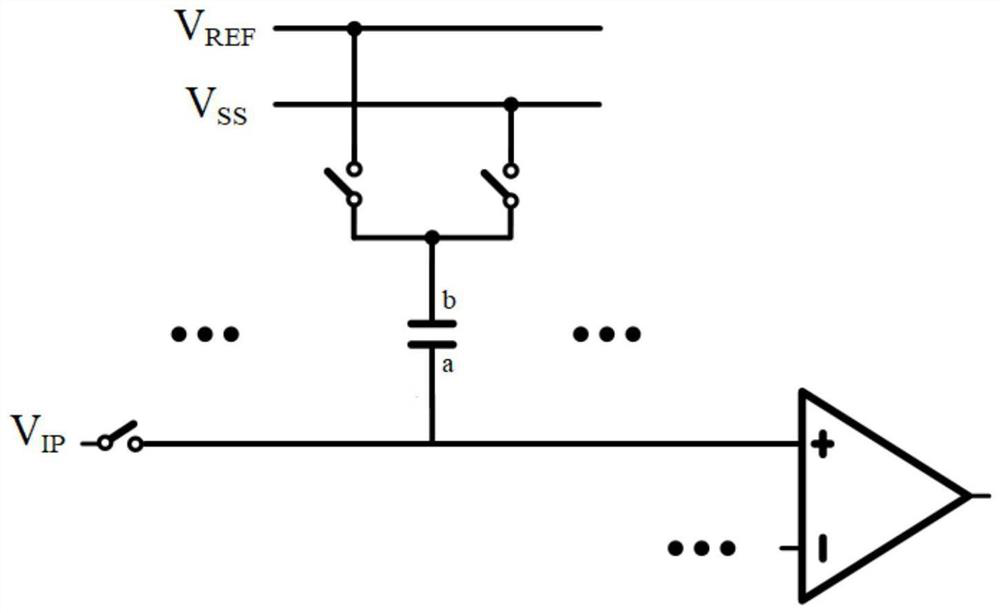

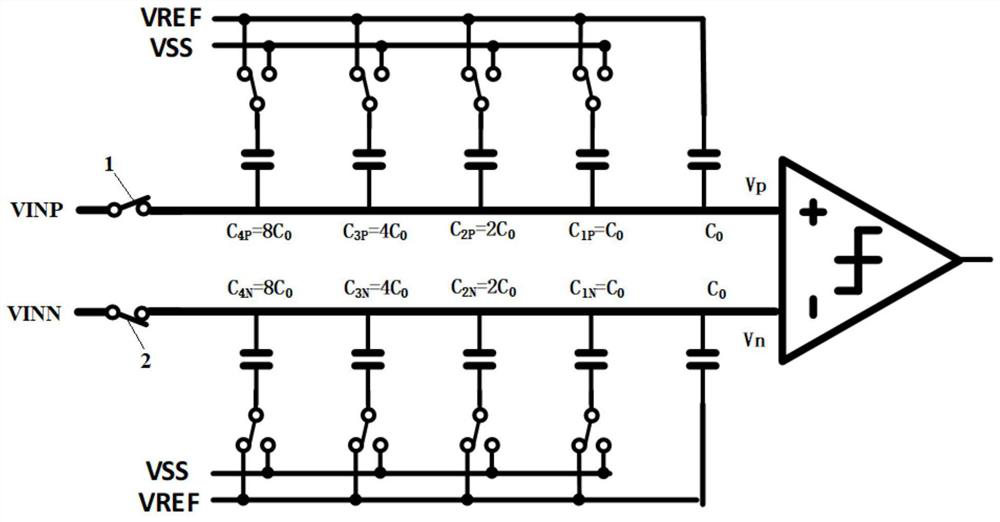

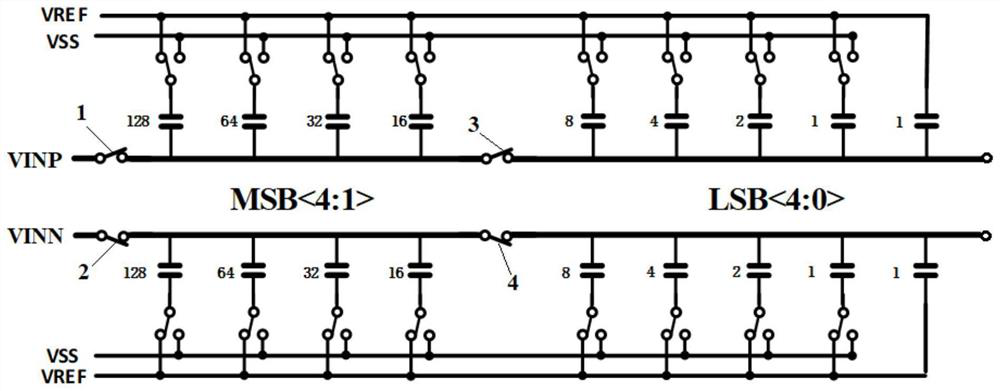

[0056] An embodiment of the present invention proposes a DAC capacitor array, such as image 3 and Figure 4 As shown, the DAC capacitor array includes: a first capacitor array and a second capacitor array; the first capacitor array includes a unit capacitor and a capacitor group; each capacitor in the capacitor group is divided into m times of 2 according to the capacitance weight The way of power is arranged in order; wherein, m is a non-negative integer; the unit capacitance is the lowest position capacitance of the first capacitance array, and the capacitance with the largest...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com