Technological method of ONO side wall

A process method and sidewall technology, which is applied in the manufacture of electrical components, circuits, semiconductors/solid-state devices, etc., to achieve the effect of reducing the difference in sidewall width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

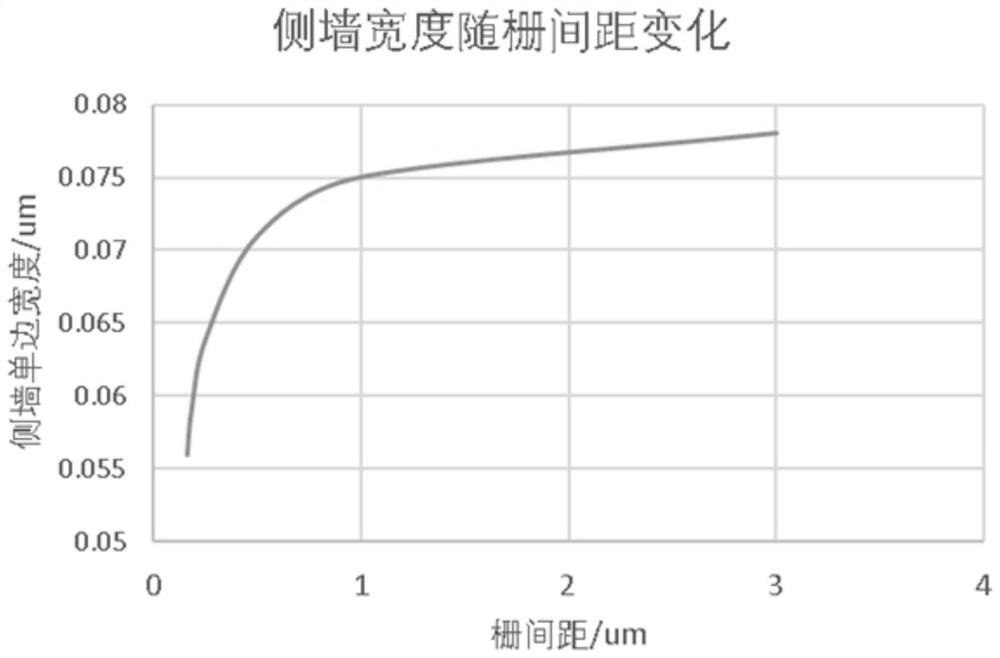

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

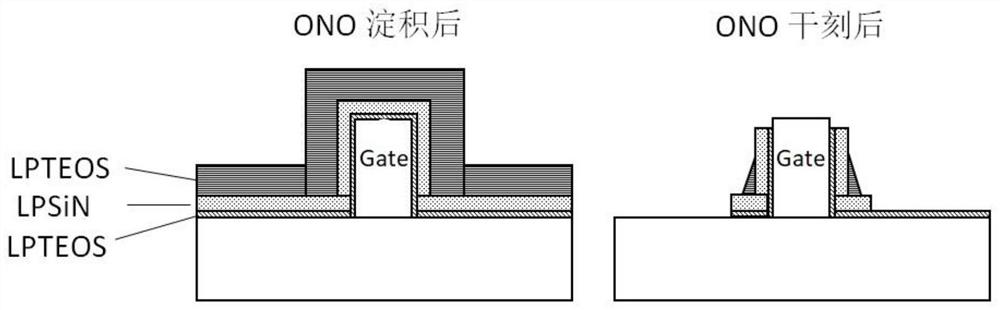

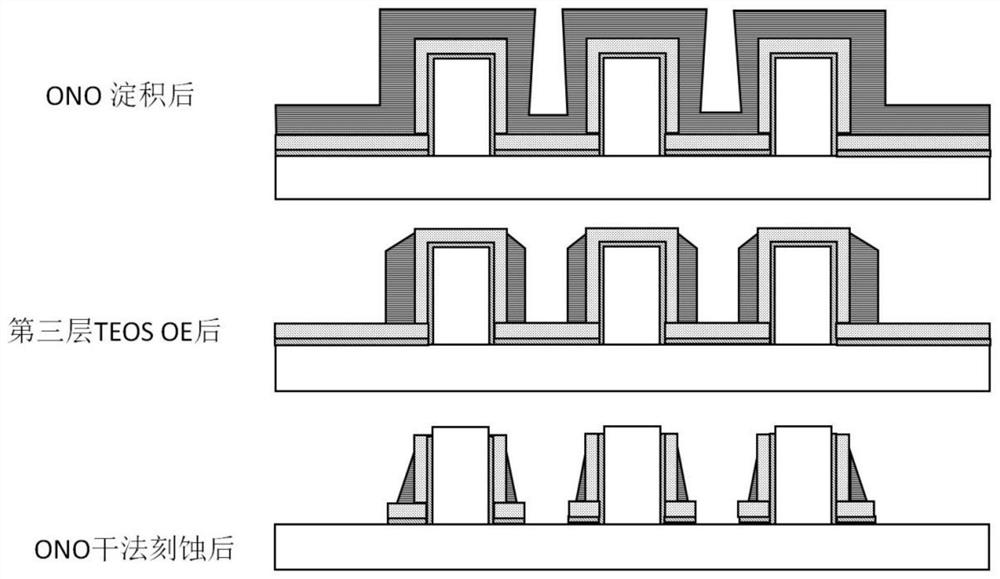

[0020] The present invention is used in the process of using the ONO structure as the side wall in the manufacture of submicron integrated circuits. The process method of the ONO side wall is described as follows in conjunction with the accompanying drawings:

[0021] After the transistors are formed on the wafer, due to the chip layout, the distribution of the transistors is uneven. The polysilicon gates of the transistors and the polysilicon gates formed by connecting the polysilicon gates constitute the dense and sparse areas of the polysilicon gates. First, the first layer, which is the innermost oxide layer, is formed using the traditional process, which is generally formed based on the LPTEOS process, with a deposition thickness of 150Å, and then the second layer, which is the middle layer of silicon nitride, is deposited using the LPCVD process. Formed to a thickness of 300Å. Therefore, depositing the first layer and the middle layer of the ONO sidewall is no different ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com