Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of affecting the normal use of three-dimensional memory devices, prone to sharp corners, insufficient filling, etc., and achieve the weakening of stress or electron attraction. Force action, avoid leakage, avoid the effect of connecting the upper and lower gate layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

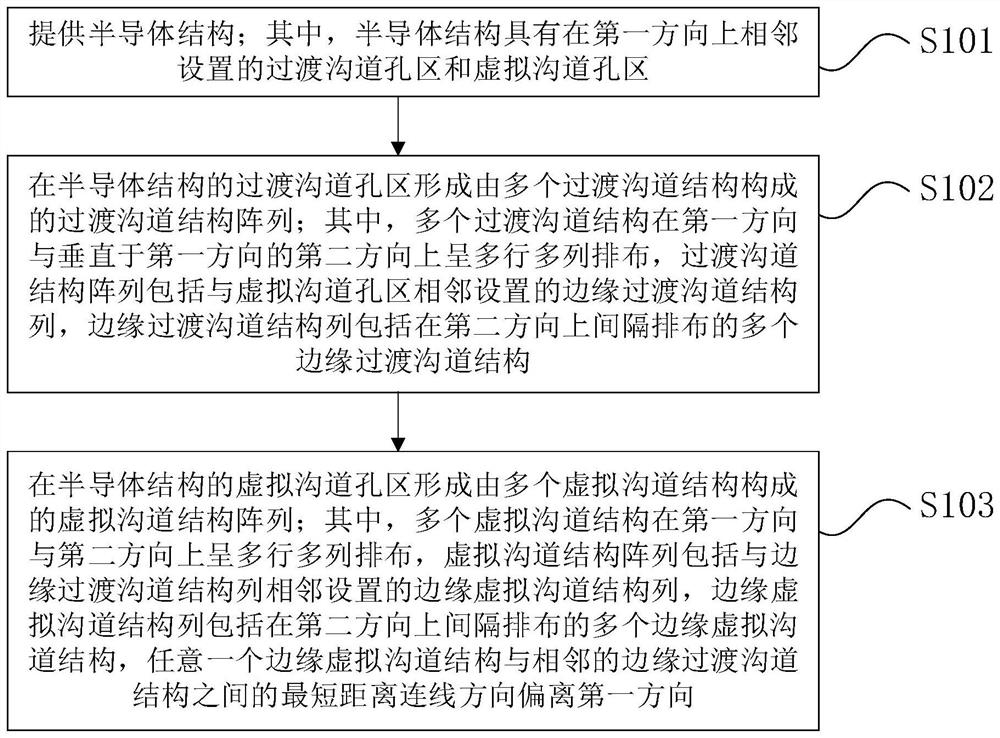

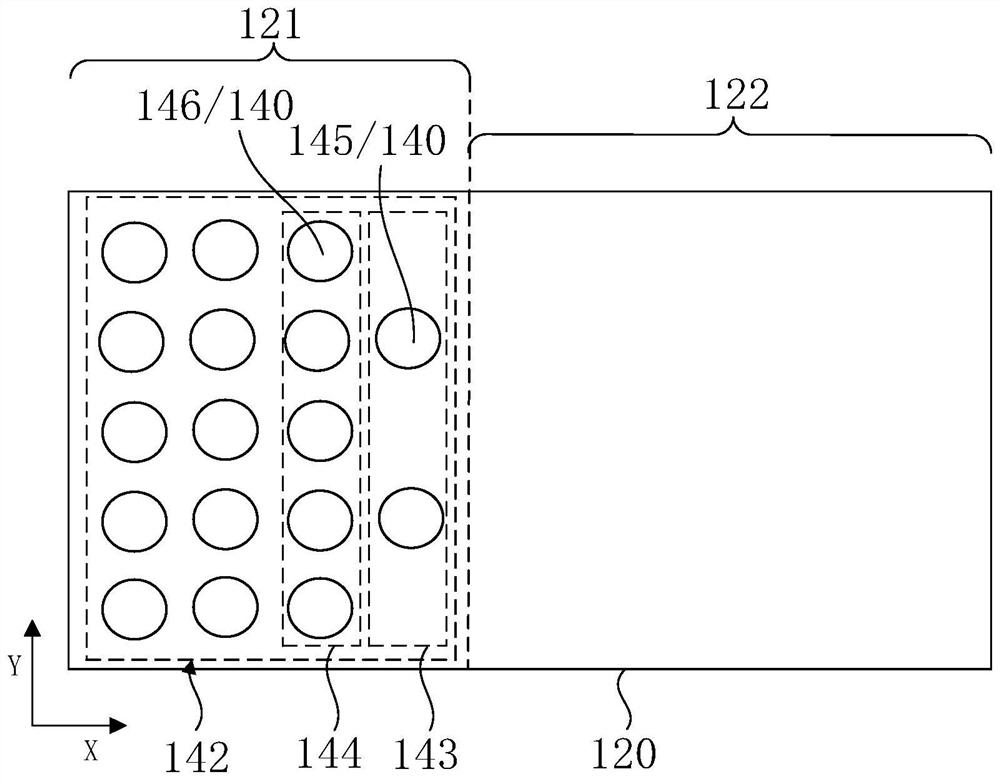

[0074] Such as figure 1 S101 in figure 2 and image 3 As shown, a semiconductor structure 120 is provided; wherein, the semiconductor structure 120 has a transition channel region 121 and a dummy channel region 122 adjacently arranged in a first direction.

[0075] Specifically, the semiconductor structure 120 includes a substrate 110 and a stack structure 123 on the substrate 110 . The first direction in this embodiment is the X direction in the figure, and the first direction is parallel to the upper surface of the substrate 110 , and the upper surface of the substrate 110 is a surface in contact with the stacked structure 123 .

[0076] The substrate 110 may include a silicon substrate, a germanium (Ge) substrate, a silicon germanium (SiGe) substrate, an SOI substrate, or a GOI (Germanium-on-Insulator, germanium-on-insulator) substrate and the like. In other embodiments, the substrate 110 may also be a substrate including other element semiconductors or compound semicon...

Embodiment 2

[0110] Such as Figure 11 As shown, the embodiment of the present application also provides a semiconductor device 100 ′, which is different from the first embodiment above in that the multiple non-edge transition channel structures 135 in any two adjacent non-edge transition channel structure columns 134 are arranged alternately in sequence in the second direction. Moreover, a plurality of non-edge dummy channel structures 155 in any two adjacent non-edge dummy channel structure columns 154 are sequentially arranged alternately in the second direction, and are close to the non-edge dummy channel structures 152 of the edge dummy channel structure column 152. The plurality of non-edge dummy channel structures 155 and the plurality of edge dummy channel structures 153 in the channel structure column 154 are sequentially arranged alternately in the second direction.

[0111] Since the other structures of the semiconductor device 100' in the embodiment of the present application ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com