A packaging material structure layer for front connection of high junction temperature power module chips and its manufacturing method

A technology for power modules and packaging materials, which is used in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, and semiconductor devices, etc. It can solve problems such as low carrying capacity, unsuitability for industrialization, and chip failure, and reduce circuit failure. The probability of , is conducive to mass production, the effect of increasing the thickness of the copper sheet

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

[0028] The invention discloses a method for manufacturing a packaging material structure layer for front-side connection of high junction temperature power module chips, comprising the following steps:

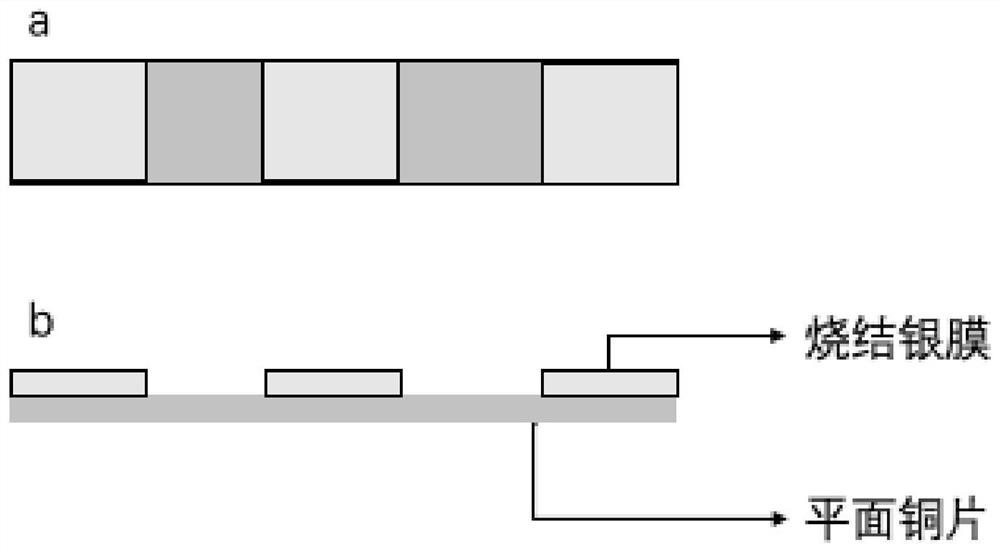

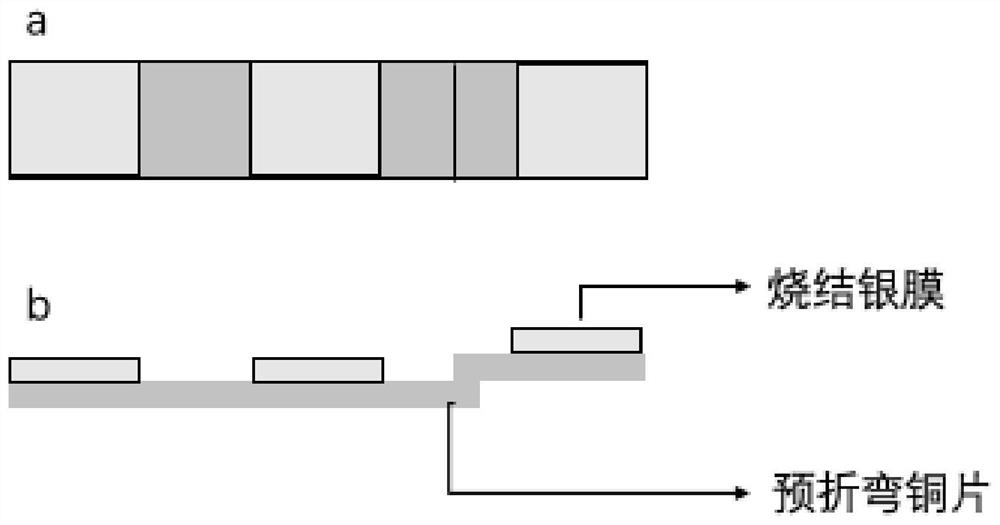

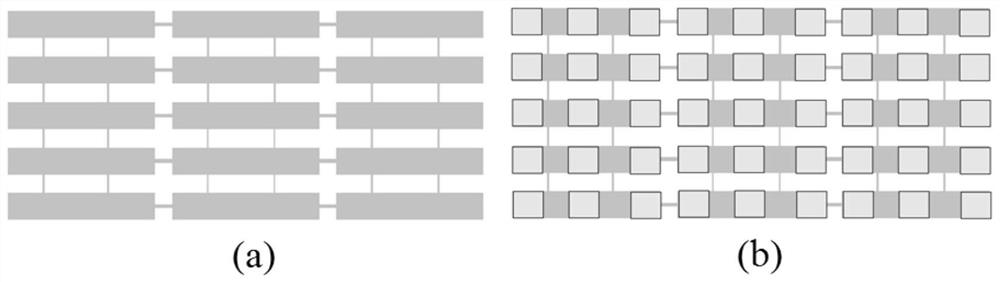

[0029] Step 1: Make a preformed planar single CSBT copper sheet or copper bar by stamping, mechanical cutting or laser cutting. The width is slightly smaller than the width of the metal pad on the front of the chip, and the thickness is 70-500 microns. The length can be based on the chip size of the package design. and interval design.

[0030] Step 2, if plating is required, silver, nickel, gold or other metal layers are plated on the copper sheets or copper bars. The chip front bonding materi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com