Method for debugging main computing core by utilizing on-chip co-computing core

A technology for computing cores and debugging hosts, applied in general-purpose stored program computers, computing, computers, etc., and can solve problems such as low efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

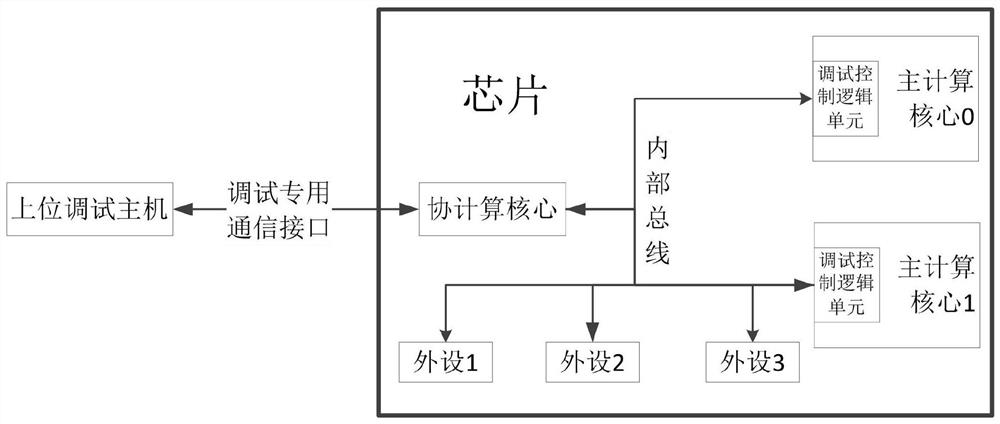

[0014] As the co-computing core that completes some auxiliary functions, it has the ability to control the on-chip peripheral resources, control the Ethernet interface, UART interface or other communication interfaces to communicate with the host computer. Internally, the co-computing core connects each peripheral device and each main computing core through an internal bus; externally, it controls the peripheral devices communicating with the upper computer, such as Ethernet interface, UART interface, etc., such as figure 1 shown. The present invention designs a method for debugging the main computing core by utilizing the on-chip co-computing core based on the characteristics of the co-computing core itself.

[0015] The co-computing core communicates with the debugging host through a communication interface used solely for debugging, analyzes the debugging commands sent by the debugging host, and converts them into operation sequences on the internal bus of the chip, and con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com