PCB processing method based on crimping holes and PCB

A technology of PCB board and processing method, applied in the field of PCB design, can solve the problem that the space occupied by holes is not used and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

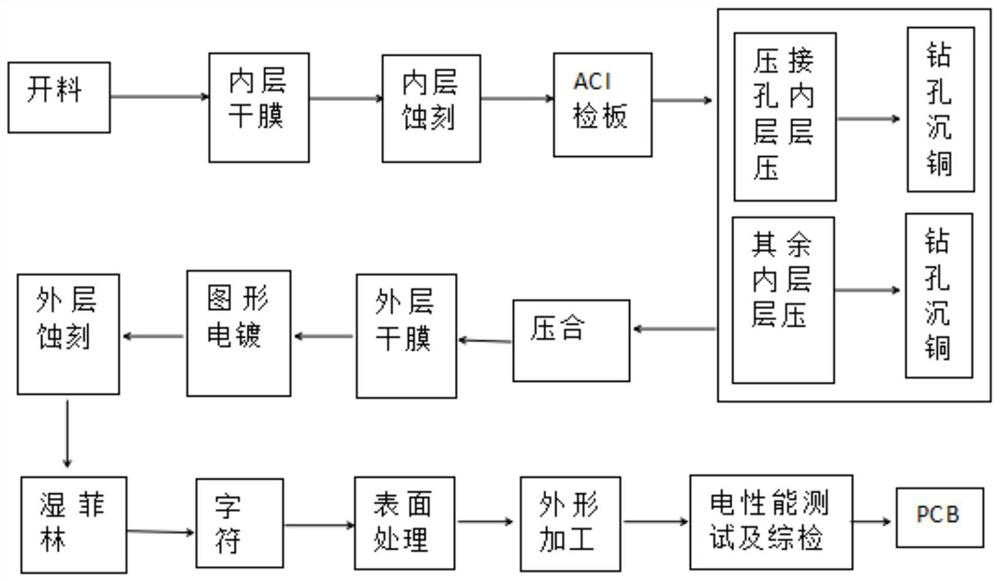

[0035] Please refer to figure 2 , the present embodiment provides a PCB board processing method based on crimping holes, comprising the following steps:

[0036] S1. Set the position information of the crimping hole on the PCB design graphic, and calibrate the effective layer of the crimping hole. The effective layers of the crimping hole in this embodiment are all three upper surface layers. The lower half area except the effective layer can be normally designed for routing, and the routing does not need to bypass the position of the crimping hole.

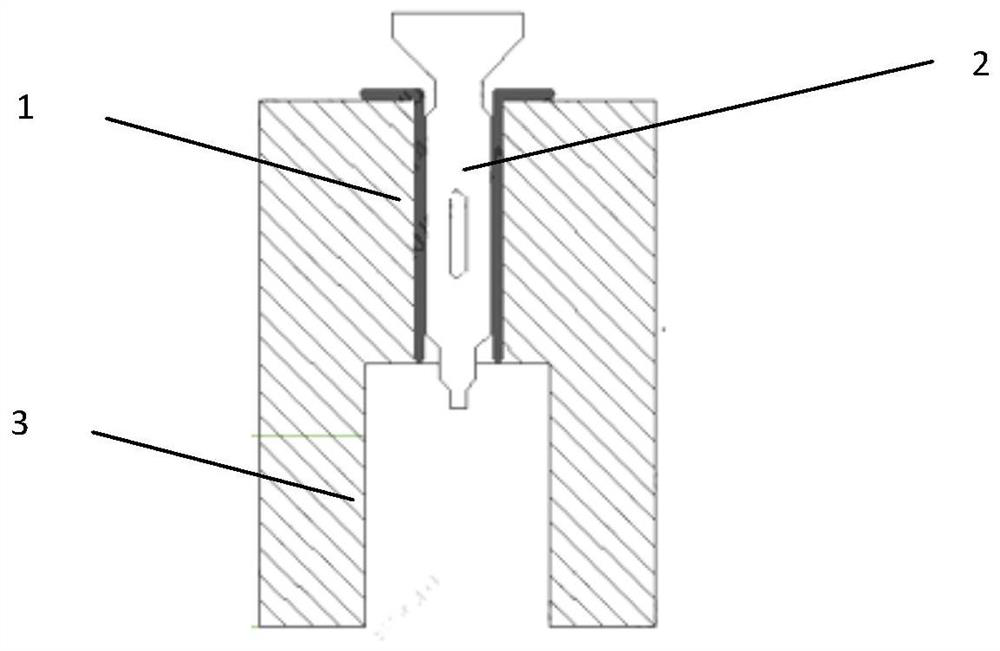

[0037] S2. Firstly, process the material cutting, memory dry film, memory etching and ACI board inspection process for each layer of the PCB board. The effective layer is laminated into the first sub-board, and copper is drilled on the first sub-board, and the size of the drill hole matches the pin of the crimper. According to the PCB design pattern, press the lower half of the PCB board to obtain the second sub-board, and dr...

Embodiment 2

[0040] This embodiment provides a PCB board processing method based on crimping holes, comprising the following steps:

[0041] Compared with Example 1, if the number of effective layers of PCB holes is different, the method of splicing and stacking is used to prepare the PCB. For example, there are two kinds of drill holes, drill hole 1 is the third floor in the upper half area, and drill hole 2 is the fifth floor in the upper half area. Firstly, press the three-layer boards in the upper half area to obtain the first sub-board, and drill holes at the corresponding positions of the drilling holes 1 on the first sub-board. The remaining two layers of the drilled hole 2 are superimposed and pressed on the first sub-board to obtain a second sub-board, and copper sinking is performed on the corresponding position of the drilled hole 2 of the second sub-board.

Embodiment 3

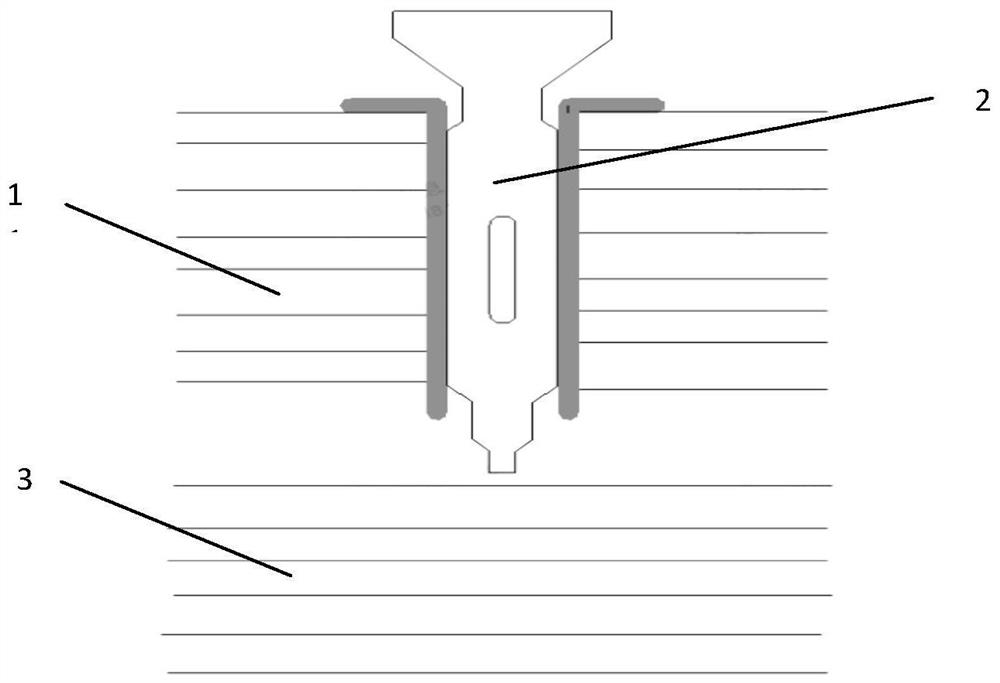

[0043] Please refer to image 3 , this embodiment provides a PCB board. The crimping hole of the PCB board provided in this embodiment is only drilled on the effective layer, and the hole matches the pin size of the crimping device. There are no drill holes on the board layer of the PCB board that is not in contact with the pins of the crimper, and the wiring can be routed normally.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com