Charge pump and active loop filter with shared unity gain buffer

A unit-gain buffer, charge pump technology, applied in electrical components, automatic power control, conversion equipment without intermediate conversion to AC, etc., can solve problems such as increased cost, high power, and large die area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

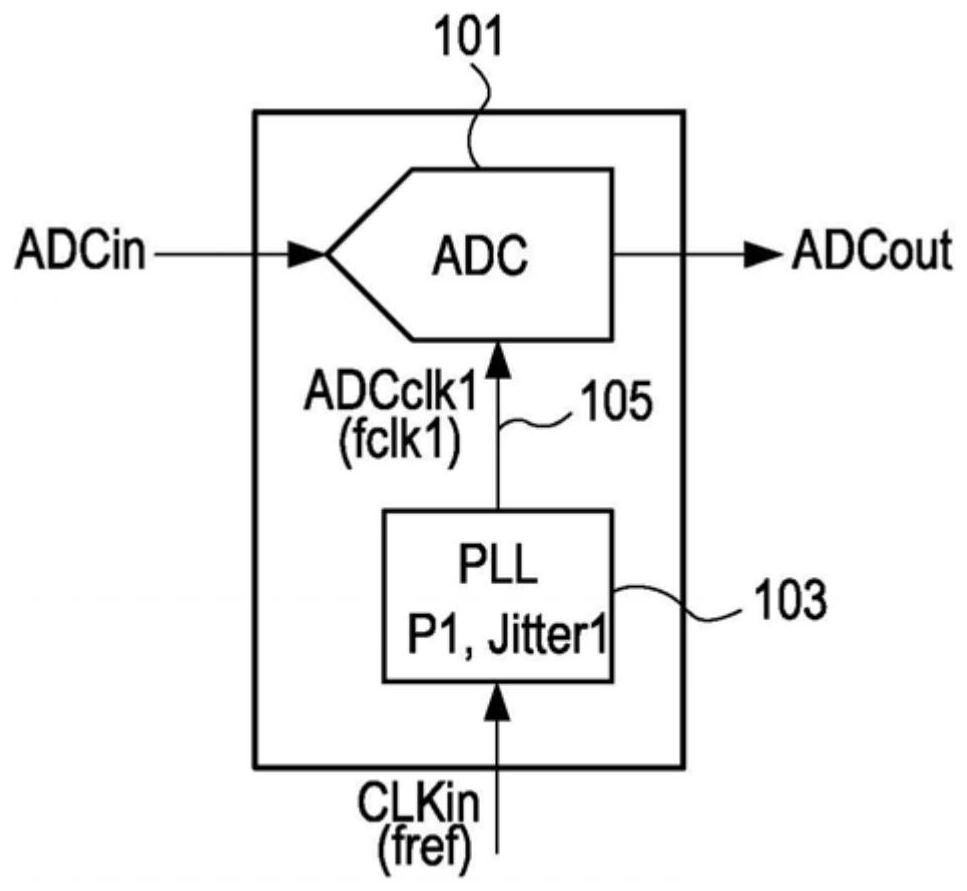

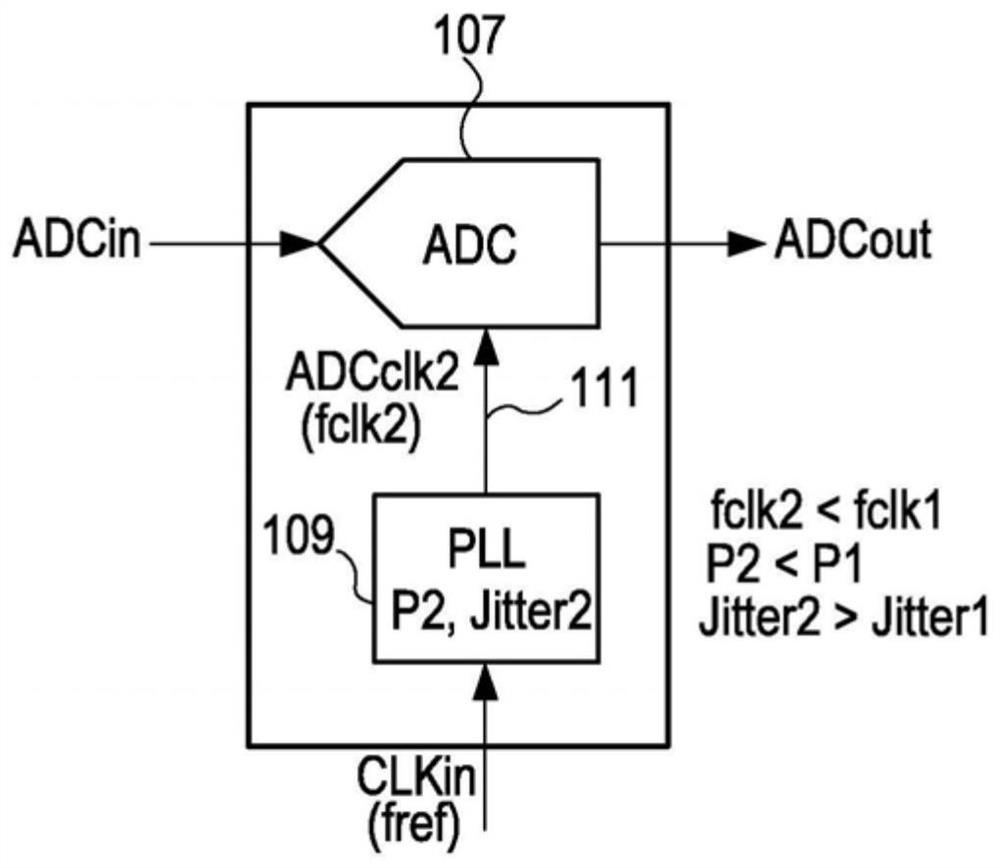

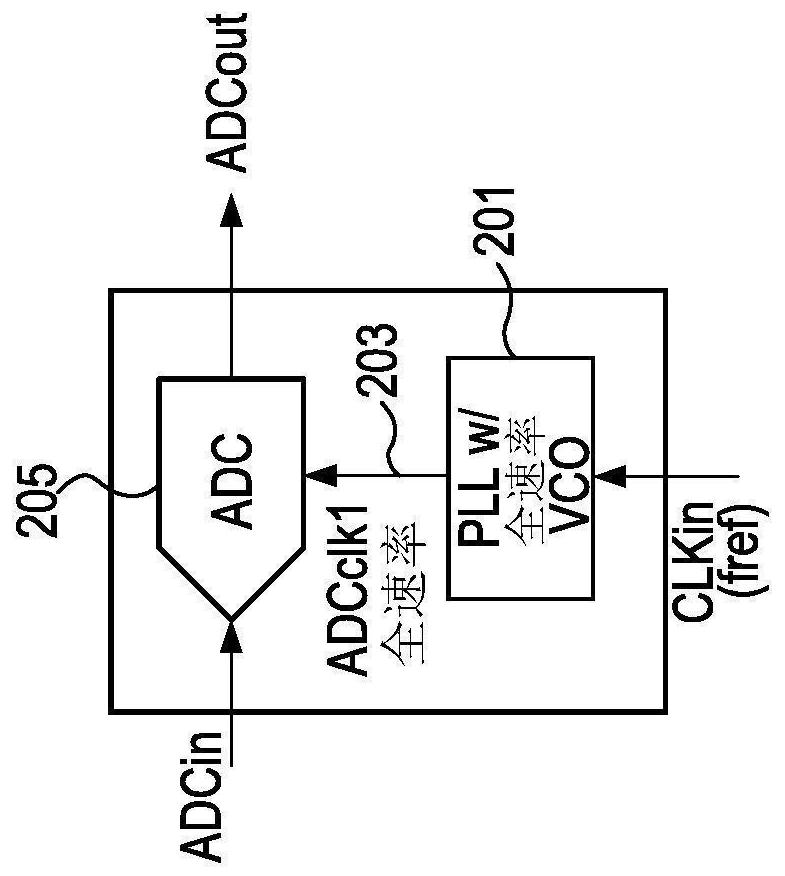

[0030] Embodiments described herein provide a phase-locked loop (PLL) specifically targeted for clock generation of a continuous time delta-sigma modulator ADC in a radio frequency receiver (RF RX) signal chain. For a given power budget, the PLL minimizes far-end phase noise at the expense of looser closure in phase noise. PLLs can also be used in other applications. Embodiments provide a variable power consumption PLL, wherein PLL power consumption is selected based on ADC requirements. For example, the PLL power can be scaled based on the input signal strength to the RX signal chain and / or based on the required clock rate of the ADC. Embodiments provide a fixed rate clock to the ADC, thereby avoiding the complexity of using a divided LO clock, thereby simplifying the design of the modem.

[0031] In one embodiment, for a 2MHz bandwidth, the ADC clock rate is approximately 307.2MHz. The integrated ADC noise bandwidth of 2MHz is mainly used for Zigbee applications. An ADC ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com