Manufacturing method of semiconductor structure

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problem that the performance of 3D packaging structure needs to be improved, and achieve the effect of preventing wrong cutting and improving performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] It can be seen from the background art that the performance of the existing 3D semiconductor structure needs to be improved.

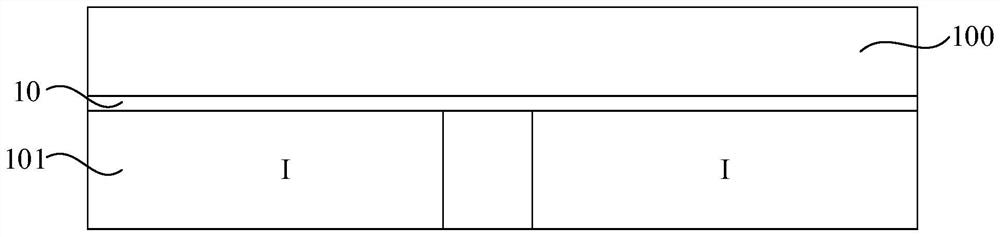

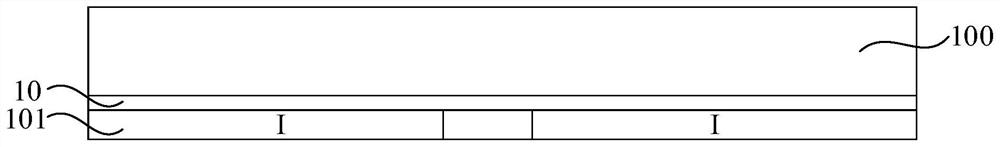

[0016] According to the analysis, it is found that the existing chip stacking (stack die) method is usually: first cut a single wafer to form chips, and then stack the cut chips on another wafer. This method is called chip on wafer. The method of Chip on wafer has complicated process steps and correspondingly higher cost. Therefore, it is hoped to propose a new cutting scheme, which is to stack multiple wafers and then perform single cutting.

[0017] However, further analysis found that as the number of stacked wafers in the 3D semiconductor structure increases, the thickness of the stacked semiconductor structure becomes thicker and thicker. It is difficult to effectively cut the semiconductor structure with a single cutting process, and it is easy to cause miscutting of the chip, especially When there is a large alignment error between wafers...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com