Manufacturing method of multilayer circuit board

A technology for multilayer circuit boards and manufacturing methods, which is applied in the fields of multilayer circuit manufacturing, printed circuit manufacturing, and printed circuits, and can solve difficulties in satisfying multilayer board manufacturing, board thickness or plating thickness-to-diameter ratio capacity limitations, and finished board warping Qu and other questions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

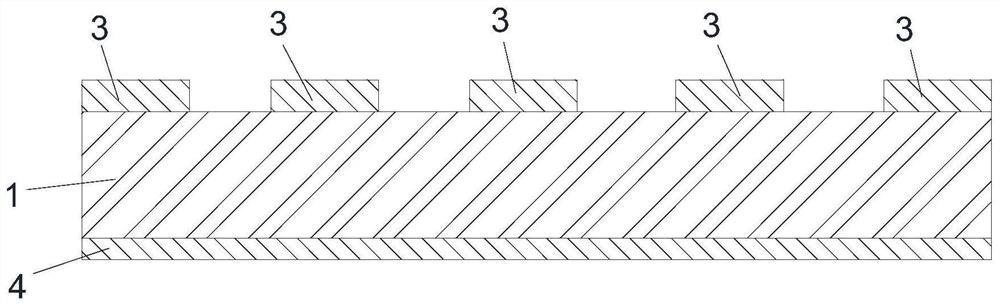

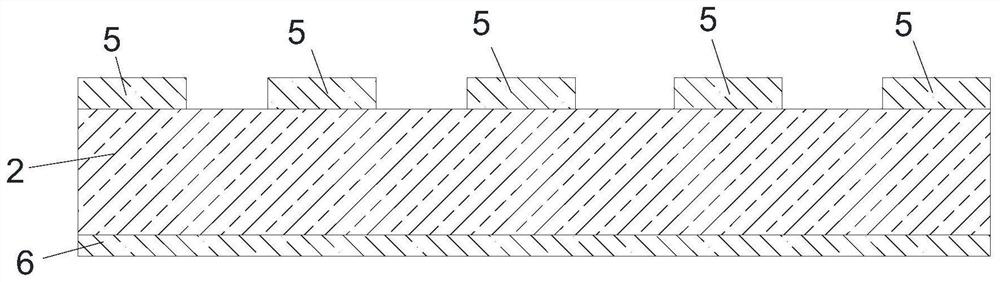

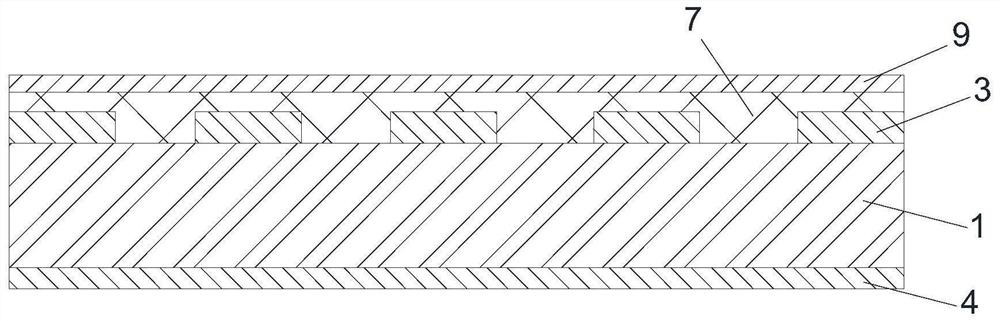

[0039] Such as Figure 1 to Figure 9 As shown, the manufacturing method of the multilayer circuit board in this embodiment, this embodiment illustrates that the multilayer circuit board with asymmetric structure can be manufactured using the method of the present invention. First, divide the target multilayer circuit board into two sub-boards, and the two sub-boards are asymmetrical to each other, for example, as figure 1 As shown, the first sub-board 1 is an arbitrary layer interconnection structure, such as figure 2 As shown, the second sub-board 2 is a through-hole interconnection structure. Each of the first sub-board 1 and the second sub-board 2 has a symmetrical structure, and the first sub-board 1 and the second sub-board 2 are respectively manufactured according to conventional methods. The first sub-board 1 has a graphics layer 3 on the side A. The second sub-board 2 has a C-surface graphics layer 5 . The method for making a multilayer circuit board includes cond...

Embodiment 2

[0052] Such as Figure 10 As shown, the manufacturing method of the multilayer circuit board in this embodiment, this embodiment also illustrates that the multilayer circuit board with an asymmetric structure can be manufactured using the method of the present invention. , and two sub-boards with different numbers of layers as an example. First, the target multilayer circuit board is divided into two sub-boards, namely the third sub-board 13 and the fourth sub-board 14, the third sub-board 13 is a 10-layer board with any layer interconnection structure, the thickness is 2mm, and the fourth sub-board 14 It is a 6-layer board with a through-blind hole interconnection structure and a thickness of 0.5mm. The third sub-board 13 has an E-side graphic layer 15 , and the fourth sub-board 14 has an F-side graphic layer 16 . The third sub-board 13 and the fourth sub-board 14 are respectively fabricated using conventional techniques. The conduction and interconnection method of the th...

Embodiment 3

[0062] Such as Figure 11 As shown, in this embodiment, the thickness of the target multilayer circuit board is 6mm as an example, which exceeds the capability of the equipment. Therefore, the target multilayer circuit board is divided into three sub-boards with a thickness of 2 mm that can be produced by the equipment, that is, the fifth sub-board 19 , the sixth sub-board 20 and the seventh sub-board 21 . The fifth sub-board 19 , the sixth sub-board 20 and the seventh sub-board 21 are respectively manufactured by conventional methods. Then, the fifth sub-board 19, the sixth sub-board 20 and the seventh sub-board 21 are conducted and interconnected, and the method for conducting and interconnecting the fifth sub-board 19, the sixth sub-board 20 and the seventh sub-board 21 includes steps:

[0063] Step 1, with reference to embodiment 1, the first adhesive sheet 7, the second adhesive sheet 8 and the isolation layer 10 are sequentially arranged on the L surface graphic layer 2...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Shore hardness | aaaaa | aaaaa |

| Shore hardness | aaaaa | aaaaa |

| Shore hardness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com