Method and device for constructing virtual video based on FPGA, storage medium and equipment

A technology in virtual video and video, applied in the computer field, can solve the problems of inability to build virtual video, high power consumption, etc., and achieve good real-time performance and low delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

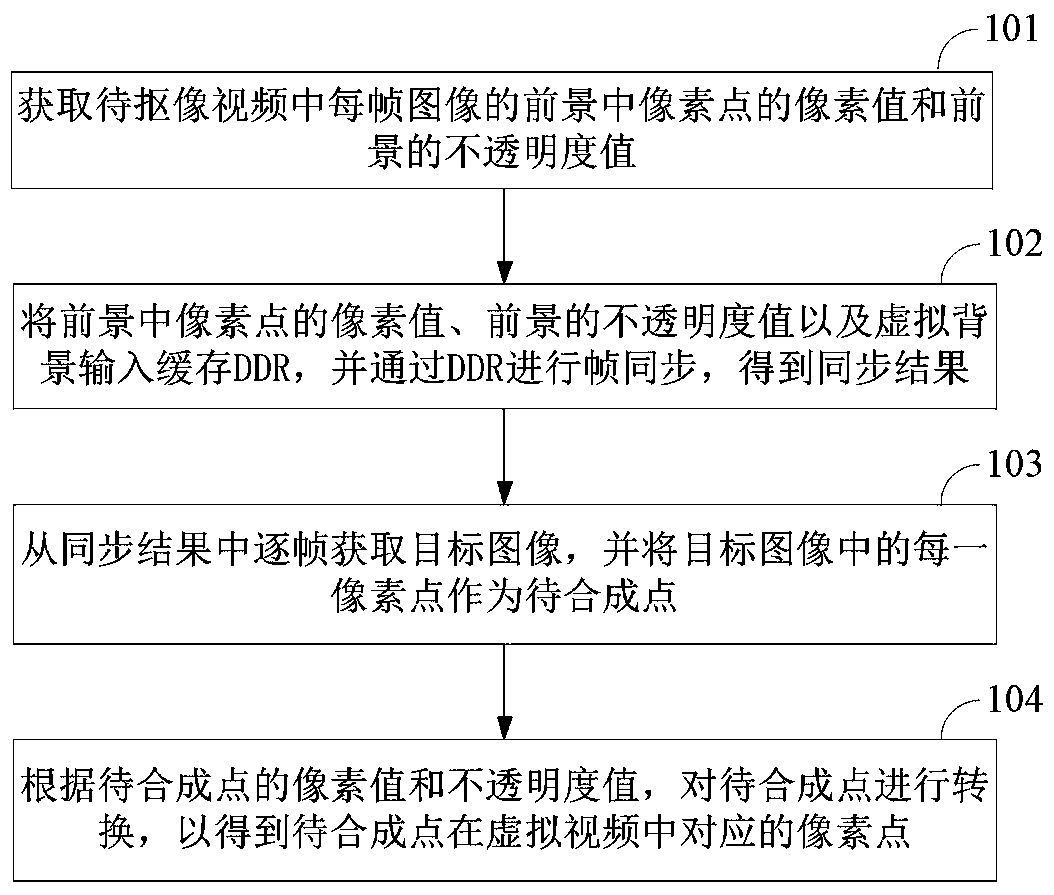

[0061] see figure 1 , a schematic flow diagram of a method for constructing a virtual video based on FPGA provided in this embodiment, the method is applied to an FPGA chip, and specifically includes the following steps:

[0062] S101: Obtain the pixel value of the pixel point in the foreground and the opacity value of the foreground of each frame of image in the video to be keyed.

[0063] In this embodiment, any video for virtual video construction using this embodiment is defined as a video signal to be keyed. Each frame of the video to be keyed includes a background and a foreground where a target composite object (such as a person or a vehicle, etc.) is located. Further, existing or future image keying methods can be used to perform keying processing on each frame of the video to be keyed. For example, the method of chroma key keying can be used to perform keying processing on each frame of image, so as to accurately obtain The pixel values of the pixels in the backgr...

no. 2 example

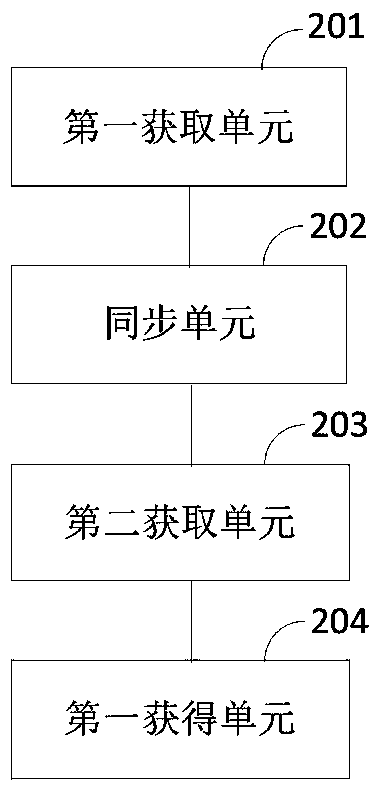

[0141] This embodiment will introduce an FPGA-based device for constructing a virtual video. For related content, please refer to the foregoing method embodiments.

[0142] see figure 2 , which is a schematic composition diagram of a device for constructing virtual video based on FPGA provided in this embodiment. The device is applied to an FPGA chip, and specifically includes:

[0143] The first obtaining unit 201 is used to obtain the pixel value of the pixel point in the foreground of each frame of image in the video to be keyed and the opacity value of the foreground;

[0144] A synchronization unit 202, configured to input the pixel value of the pixel in the foreground, the opacity value of the foreground, and the virtual background into the cache DDR, and perform frame synchronization through the DDR to obtain a synchronization result;

[0145] The second acquisition unit 203 is configured to acquire the target image frame by frame from the synchronization result, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com